# Telecom Design Solutions

| 1. | CUSTOMER INFORMATION                                                                                                                                                                                                                                                                                                                                                             |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | Teltone Corporation                                                                                                                                                                                                                                                                                                                                                              |

| 2. | SELECTION GUIDES                                                                                                                                                                                                                                                                                                                                                                 |

|    | DTMF Receivers and Transmitters                                                                                                                                                                                                                                                                                                                                                  |

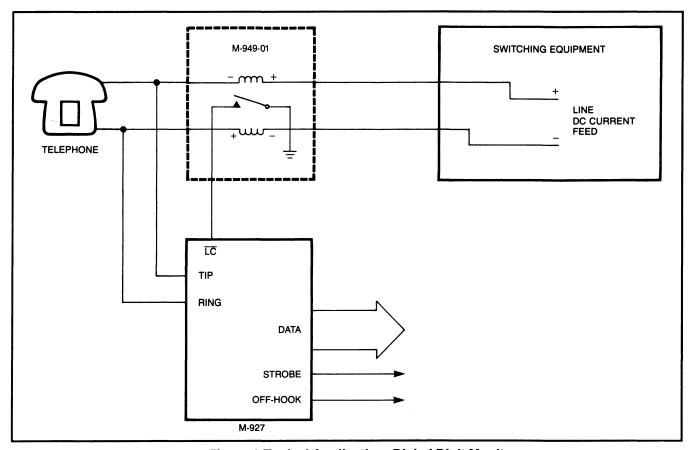

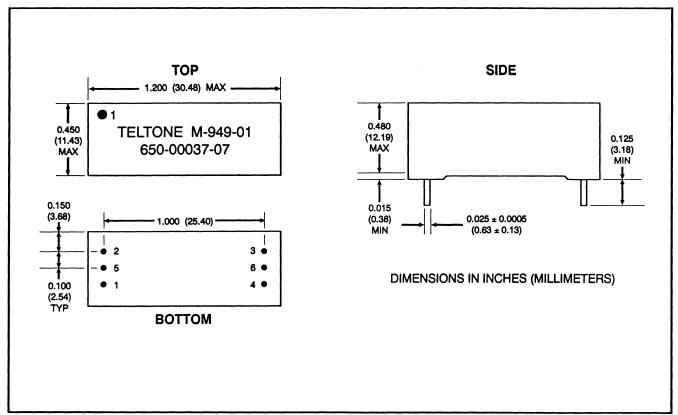

| 3. | DTMF RECEIVERS AND TRANSMITTERS                                                                                                                                                                                                                                                                                                                                                  |

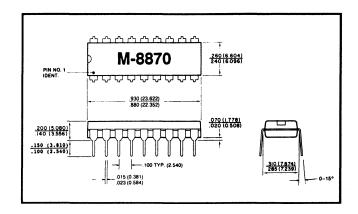

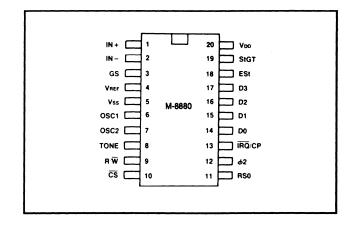

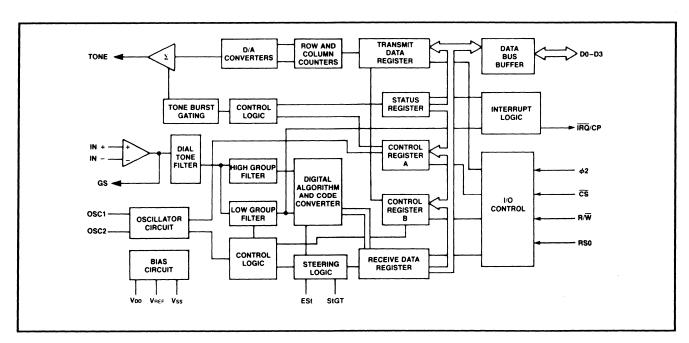

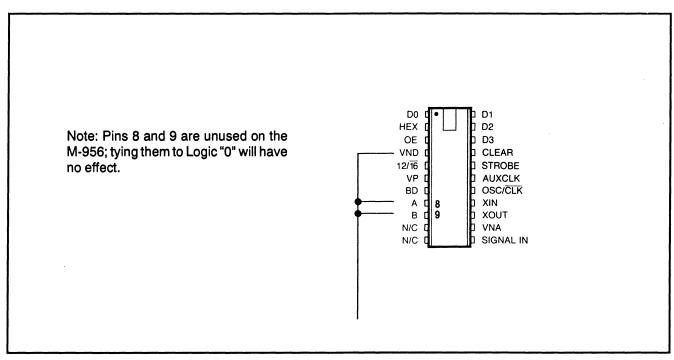

|    | M-957-01 DTMF Receiver       .3-1         M-957-02 DTMF Receiver       .3-9         M-8870 DTMF Receiver       .3-17         M-8880 DTMF Transceiver       .3-25         M-8888 DTMF Transceiver       .3-37                                                                                                                                                                     |

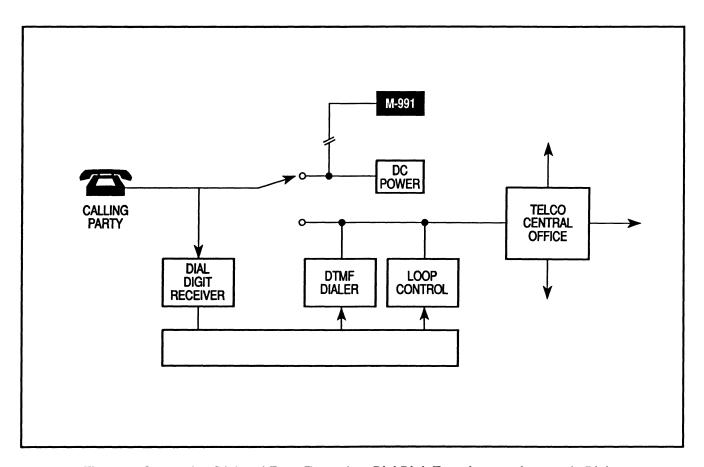

| 4. | CALL PROGRESS TONE RECEIVERS AND TRANSMITTERS                                                                                                                                                                                                                                                                                                                                    |

|    | M-980 General Purpose Call Progress Tone Detector M-981 Precise Call Progress Tone Detector M-982 Precise Call Progress Tone Detector M-984 Special Tone and Call Progress Tone Detector M-991 Call Progress Tone Generator  4-15 4-19                                                                                                                                           |

| 5. | MF TRUNK RECEIVERS AND TRANSMITTERS                                                                                                                                                                                                                                                                                                                                              |

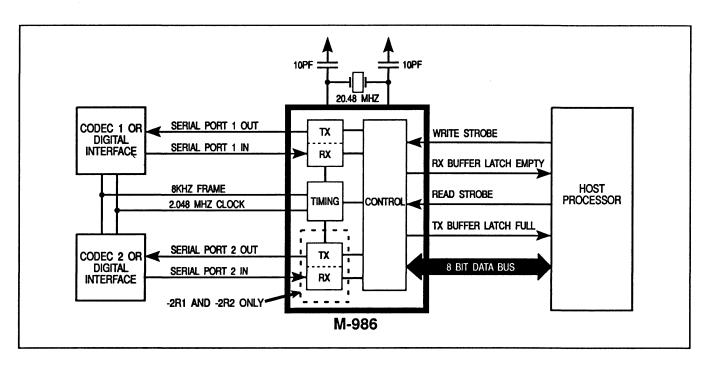

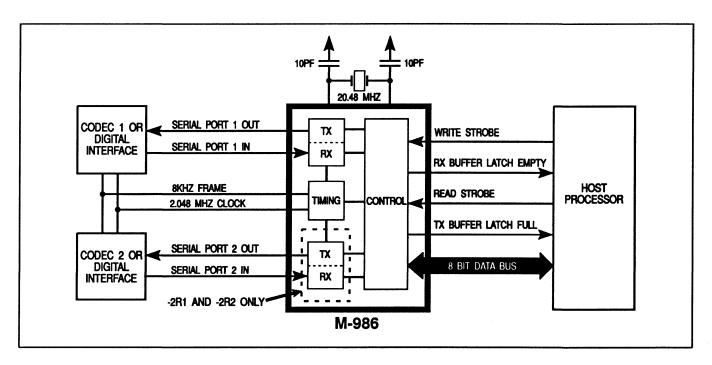

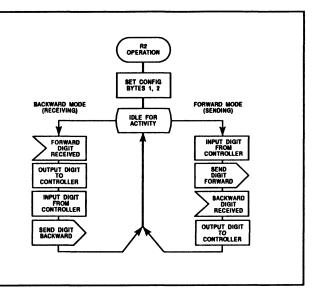

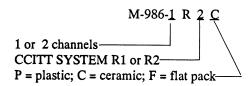

|    | M-986-1R1 and -2R1 MF Transceivers                                                                                                                                                                                                                                                                                                                                               |

| 6. | DC SIGNALING DEVICES                                                                                                                                                                                                                                                                                                                                                             |

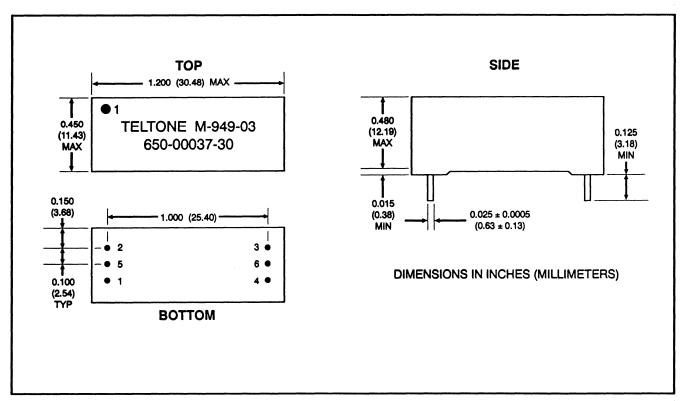

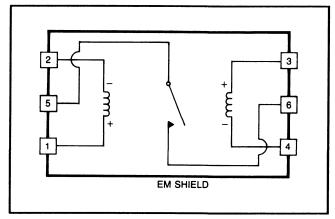

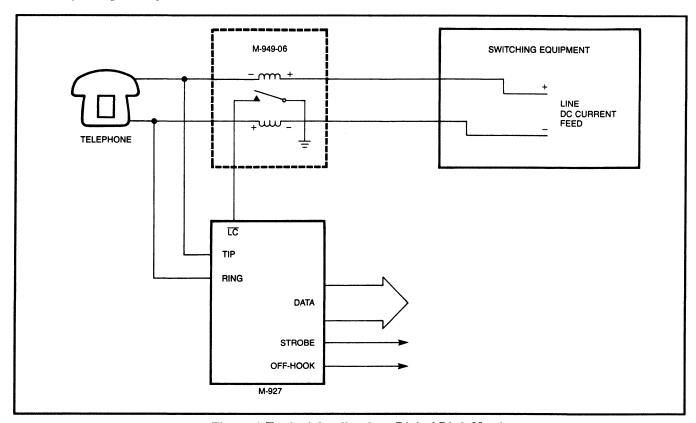

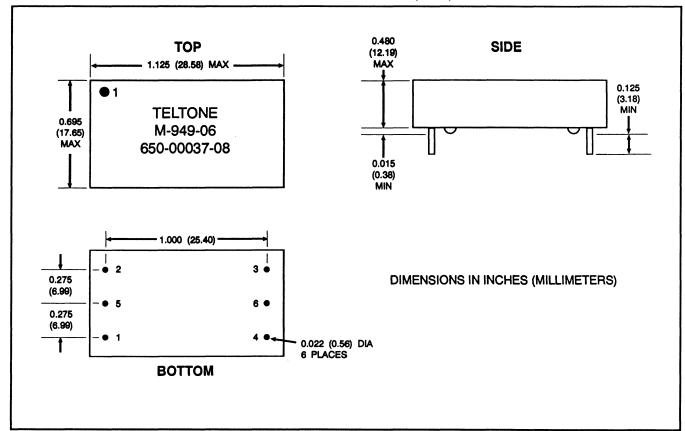

|    | M-949-01 Line Sense Relay       6-1         M-949-02 High-Breakdown Line Sense Relay       6-3         M-949-03 Line Sense Relay       6-5         M-949-06 High-Breakdown Line Sense Relay       6-7         M-949-10 Line Sense Relay       6-9         M-959 Dial Pulse Counter and Hook Status Monitor       6-11                                                            |

| 7. | SUSTAINED PRODUCTS                                                                                                                                                                                                                                                                                                                                                               |

|    | M-900 DTMF Filter and Decoder Set       .7-1         M-907 Tone Detector and Rotary Dial Pulse Counter       .7-13         M-917 DTMF Decoder and Dial Pulse Counter Set       .7-23         M-927 DTMF Receiver       .7-29         M-937 High-Performance DTMF/Dial Pulse Receiver       .7-35         M-947 DTMF Receiver       .7-43         M-956 DTMF Receiver       .7-49 |

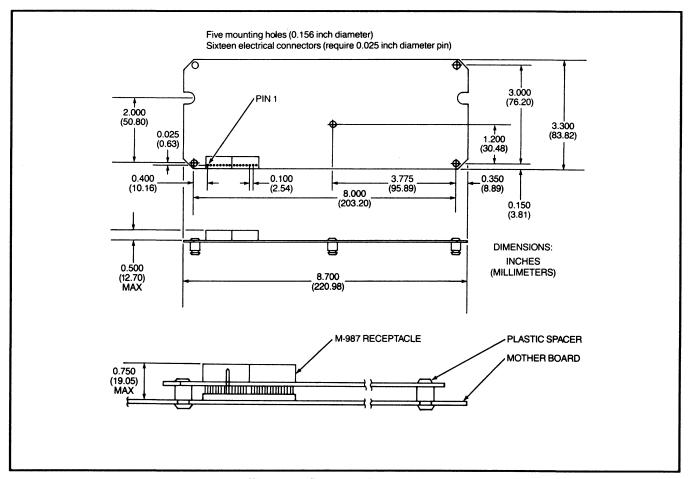

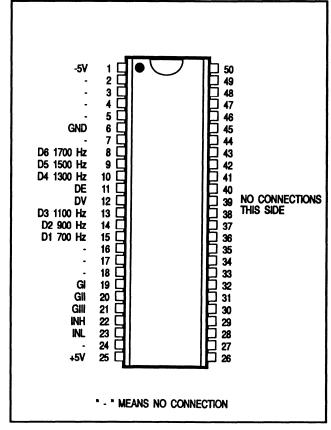

|    | M-967 DTMF Receiver       7-57         M-985 MF R1 Receiver       7-65         M-987 MF R2B Receiver       7-67         M-988 MF R1 Receiver       7-69         M-989 MF R2F Receiver       7-73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8. | TELECOM SOLUTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | Add Interoffice Calling to 1A/10A Series Key Telephone Systems.8-1Access to Office Telephone Services, Away from the Office: M-106 Remote Service Access Unit.8-3Two-Way Touch-Tone/ASCII Communications: T-310 Telephone Access Unit.8-5Demo or Test Fax Machines, Phones, and Modems: TLS-3 Telephone Line Simulator.8-7Solutions for Extending the Life of Your Key or PBX System.8-9Central Office Switch Enhancements and Service Evaluation Systems.8-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9. | APPLICATION NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|    | SC-1 Applications for DTMF and Pulse Telephone Dialing AN01 Applications for the M-980 Call Progress Tone Detector AN02 An Algorithm for Call Progress Following with the M-980 9-25 AN03 Handling MOS Devices 9-27 AN04 Third Tone Immunity and the M-957 AN05 Comparing the M-949 Line Sense Relay to Optocouplers for Loop Current Sending AN06 Current Sources of Information on Bell Technical Standards 9-33 AN07 Typical Connections for the M-957 DTMF Receiver 9-35 AN08 Rotary Dial or Pulse Dialing in Phone Systems 9-37 AN09 Call Progress Tone Standards 9-41 AN13 Using a PBX to Implement a Manufacturing Tracking System 9-45 AN14 An Application for the M-991 Call Progress Tone Generator 9-47 AN15 Interchangeability of the Teltone M-956 and M-957 AN16 Applications for Teltone Components in Private Pay Stations 9-51 AN20 A Two-IC Alternative to the M-958 PCM DTMF Receiver 9-55 AN31 Use of the Teltone TLS-3 in Fax Dealership/Phone Store Applications 9-57 AN32 Baud Rate Adjustment for the T-310 |

# Section 1

# Customer Information

# TELTONE CORPORATION

Teltone, a Seattle-area company, has been developing innovative products to meet the needs of the telecommunications industry since it was founded in 1968. Our Telecom Components division offers a wide spectrum of telecommunications components, including state-of-the-art tone receivers, detectors, and other signaling products.

An early product area, DTMF-to-rotary dial conversion equipment, brought us leadership status in subscriber dialing and has resulted in the development of a complete family of tone receivers for use by manufacturers of PBXs, security and control devices, and many other types of equipment. Our experience with signaling technology in our own conversion, remote access, and service evaluation products has made Teltone components performance leaders in the domestic and international markets.

Over the years, Teltone has gained a reputation for commitment to quality, reliability, and customer service. The accumulation of more than 20 years' experience working with telephone companies, interconnects, government agencies, and large and small businesses, has taught us the importance of being responsive to the demands and problems of a variety of customers.

# NORTH AMERICAN DISTRIBUTORS

#### **ALLIANCE ELECTRONICS**

Albuquerque, NM Phone: 505-292-3360 Fax: 505-275-6392

#### **ALMO ELECTRONICS**

(Formerly Pacesetter Electronics, Inc.)

#### West

San Jose, CA Phone: 408-436-8822 Fax: 408-436-8928

Santa Ana, CA Phone: 714-757-0444 Fax: 714-757-0410

#### East

Westwood, MA Phone: 617-329-2555 Fax: 617-329-3202

Wallingford, CT Phone: 203-269-6801 Fax: 203-269-6527

E. Brunswick, NJ Phone: 201-613-0200 Fax: 201-613-9689

Mars, PA

Phone: 412-776-9090 Fax: 412-776-0299

Trevose, PA

Phone: 215-953-2899 Fax: 215-364-4928

Jessup, MD

Phone: 301-953-2566 Fax:301-953-0039

#### **AXIS ELECTRONICS**

Gaithersburg, MD Phone: 301-840-9640 Fax: 301-840-9299

#### **BELL COMPONENT SALES**

Arlington, TX Phone: 817-461-5303 Fax: 817-861-1710

#### COMPONENT DISTRIBUTORS

Clearwater, FL Phone: 813-796-0466 Fax: 813-796-0846

Dallas, TX

Phone: 214-644-0373 Fax: 241-644-1115

Englewood, CO Phone: 303-770-6214 Fax: 303-770-6057

Huntsville, AL Phone: 800-888-0331 or: 205-851-7800 Fax: 205-859-2259

Melbourne, FL Phone: 800-558-2351 (Fla. only) or: 407-724-9910 Fax: 407-729-6579

Norcross, GA Phone: 404-441-3320 Fax:404-449-1712

Raleigh, NC Phone: 919-859-3391 Fax: 919-859-3396

#### **CRONIN ELECTRONICS**

Needham, MA Phone (Nat'l Toll Free): 800-527-6646 or: 617-449-5000 New England: Phone: 800-225-4501 or: 800-225-4512 Fax: 617-444-8395

New Hampshire Phone: 603-624-0105 Fax: 603-622-7459

Wellingford, CT Phone: 203-265-3134 Fax: 203-265-6765

#### **D-HMARKETING**

Wayland, MA Phone: 800-225-8760 or: 508-655-0888 Fax: 508-655-0939

#### **GOOLD ELECTRONICS**

Bensenville, IL Phone: 800-323-6639 or: 708-860-7171 Fax: 708-860-7260

#### HIGH TECHNOLOGY SEMICONDUCTORS

Tustin, CA

Phone: 714-259-7733 Fax: 714-544-4871

#### **YANKEE DISTRIBUTORS**

Dayton, OH Phone: 800-543-3370 or: 513-890-1700 Fax: 513-890-2082

#### Canada

#### KAYTRONICS, INC.

Ville St. Laurent, Canada Phone: 514-745-5800 Fax: 514-745-5858

## NORTH AMERICAN REPRESENTATIVES

#### **TELTONE CORPORATION**

After February 1, 1991:

Bothell, WA

Phone: 800-426-3926 or: 206-487-1515 Fax: 206-487-2288 National Sales Manager:

Steve Walker

Alaska Arizona Colorado Connecticut Hawaii Idaho Illinois Indiana Iowa Kansas Kentucky Maine Maryland Massachusetts Michigan Minnesota

Missouri Montana Nebraska New Hampshire New Mexico New York (Zip 12000 and higher) North Carolina

North Dakota Ohio Oregon Pennsylvania (7in 16699 an

(Zip 16699 and lower) Rhode Island

Rhode Island South Carolina South Dakota Utah

Vermont

Virginia

Washington

Washington, D.C.

West Virginia

Wisconsin

Wyoming

#### A.C.M. CORPORATION

Huntsville, AL Phone: 205-883-9720 Fax: 205-883-5885

Norcross, GA

Phone: 404-448-7025 Fax: 404-368-1163

Alabama Georgia Mississippi Tennessee

#### **BEACON ELECTRONICS**

Boca Raton, FL Phone: 407-997-5740 Fax: 407-994-4518

Longwood, FL Phone: 407-332-1940 Fax: 407-332-1786

Florida

#### VALE ELECTRONICS

Irvine, CA

Phone: 714-551-4004 Fax: 714-551-2886

California

(Zip 93999 and lower)

#### **DANER-HAYES**

Wayland, MA

Phone: 800-225-8760 or: 508-655-0888 Fax: 508-655-0939

Delaware New Jersey New York (Zip 11999 and lower) Pennsylvania

(Zip 16700 and higher)

#### G.N.H., INC.

Mountain View, CA Phone: 415-961-6740 Fax: 415-961-4979

Sacramento

Phone: 209-223-3389

California

(Zip 94000 and higher)

Nevada

#### MILES J. COOLEY CO.

Dallas/Fort Worth, TX Phone: 214-262-5893 Fax: 214-262-5893

Arkansas Louisiana Oklahoma Texas

# INTERNATIONAL REPRESENTATIVES

#### **AUSTRIA**

Hantronic Ltd.

Phone: 43 (222) 887 171 Fax: 43 (222) 888 478

#### **BELGIUM & NETHERLANDS**

Klaasing Electronics B.V. Phone: 31 (1620) 816 00 Fax: 31 (1620) 565 00

#### CANADA

Teltone Limited Phone: (416) 475-0837 Fax: (416) 474-9151

Kaytronics, Inc. Phone: 514-745-5800 Fax: 514-745-5858

#### **DENMARK**

Inotec AS

Phone: 45 (42) 948 033 Fax: 45 (42) 948 485

#### **FINLAND**

Norecom Oy

Phone: 358 (0) 692 7877 Fax: 358 (0) 692 7172

#### HONG KONG

Weltronics Component Ltd. Phone: 852 4100 623 Fax: 852 4100 920

#### **INDIA**

Electrolink Systems Phone: 91 (812) 641 894

#### ISRAEL

RDT Electronics Engineering Ltd. Phone: 972 (3) 483 211 Fax: 972 (3) 491 190

#### **ITALY**

International Commerce

Company

Phone: 39 (2) 892 00939 Fax: 39 (2) 892 00830

#### **KOREA**

Sejin Industries, Inc. Phone: 82 (2) 782 8768 Fax: 82 (2) 784 4453

#### MALASIA & SINGAPORE

Emtel

Phone: 60 (3) 717 2200 Fax: 60 (3) 717 3840

#### **NEW ZEALAND**

Philips Components Phone: 64 (9) 894 160 Fax: 64 (9) 897 811

#### **NORWAY**

UMI A.S.

Phone: 47 (33) 86 000 Fax: 47 (33) 86 350

#### **JAPAN**

M.C.M. Japan Ltd. Phone: 81 (3) 3487 8477 Fax: 81 (3) 3487 8825

#### **PHILIPPINES**

Atronics Manufacturing

Corporation

Phone: 63 (2) 817 7150

#### **PORTUGAL**

Componenta Lda. Phone: 351 (1) 362 1283 Fax: 351 (1) 363 7655

#### **SINGAPORE**

Serial System Marketing Phone: 65-2938-830 Fax: 65-2912-673

Jireh Electronics Phone: 65 271 9629 Fax: 65 273 0405

#### **SPAIN**

Amitron S.A.

Phone: 34 (1) 247 9313 Fax: 34 (1) 248 7958

#### **SWEDEN**

Com-Trade A/B Phone: 46 (8) 370 420 Fax: 46 (8) 372 142

#### **SWITZERLAND**

Metronic AG

Phone: 41 (1) 322 8484 Fax: 41 (1) 322 6842

#### **TAIWAN**

Leadtorn Industrial Inc. Phone: 886 (2) 785 6112 Fax: 886 (2) 782 5814

#### **UNITED KINGDOM**

Chesilvale Ltd.

Phone: 44 (272) 736 166 Fax: 44 (272) 736 516

#### **VENEZUELA**

Applewhite Associates Phone: 58 (2) 572 9597

#### **GERMANY**

Allmos Electronic Phone: 49 (89) 857 2086 Fax: 49 (89) 857 3702

# TERMS AND CONDITIONS

#### PRICE

All prices contained herein are list prices, F.O.B. Teltone Corporation, Kirkland, Washington.

Prices are subject to change without notice and are exclusive of applicable taxes, duty, export or special packing, insurance, etc. Invoiced prices will be those in effect at time of shipment.

#### MINIMUM BILLING

Any order amounting to less than One Hundred Dollars (\$100.00) net, shall be billed at One Hundred Dollars (\$100.00).

#### **TERMS**

Net 30 days.

#### **WARRANTIES**

#### **SOFTWARE**

Seller warrants that the Software will perform substantially in accordance with the accompanying written manuals and specifications for a period of twelve (12) months from the date of delivery. Seller will correct any errors present in the software at the time of delivery that significantly affect performance in accordance with the specifications in written manuals. This warranty is contingent upon the Buyer promptly notifying the Seller of such errors. Such notification must be in writing and must be received by the Seller within the 12 months period following delivery. Any changes made to the Software shall be warranted as provided herein for the remainder of the original warranty period or for ninety (90) days, whichever is longer, calculated from the date the changes are received by Buyer.

#### **EQUIPMENT**

Seller warrants that all equipment sold pursuant to the agreement is free from defects in material or workmanship at the time of delivery. If Seller receives written notice of any such defects within 12 months of delivery, and if the defect is not the result of improper usage, service, maintenance, or installation by someone other than the Seller or its authorized representative, and the equipment has not been damaged or abused after delivery, or altered or modified by anyone other than an authorized employee or representative of Seller, Seller shall replace or repair (at its sole option) the defective part or parts of equipment in accordance with the following:

1. Any such defective Material shall be returned prepaid by Buyer to Sellers plant (or to any other repair facility designated by Seller), and if Seller, in its sole discretion, determines on examination that the part or parts returned contain a defect in Material or workmanship covered by this warranty, Seller shall repair or replace Material at its expense, and return ship such Material, freight prepaid. If Seller determines on examination that there is a defect in the Material returned, but that the defect

is not covered by this warranty, Seller shall notify the Buyer of the cost incurred to diagnose the defect and of the estimated cost of correcting the defect and, if requested to do so by Buyer, will correct such defect, return ship such Material, freight prepaid, and bill Buyer for cost of repair and freight.

2. Seller will, on request, furnish qualified service personnel to repair or replace under warranty any Material at any location(s) designated by Buyer. Buyer shall pay Seller for all expenses of such personnel including transportation, room, board and other travel expenses.

Any replacement or repair performed by Seller shall be warranted, as provided herein, for the remainder of the original warranty period or for ninety (90) days, whichever is longer, calculated from the date the repair is completed or the date the repair or replacement Material is delivered, as applicable. Any repair or replacement completed on-site by Seller shall be warranted, as provided herein, for the remainder of the original warranty, or ninety (90) days, whichever is longer.

#### **LIMITATION OF WARRANTIES AND REMEDIES**

SELLER SHALL NOT BE LIABLE FOR ANY INCIDENTIAL OR CONSEQUENTIAL DAMAGES INCURRED AS A RESULT OF ANY DEFECT IN ANY SOFTWARE LICENSED OR EQUIPMENT SOLD HEREUNDER. SELLERS ENTIRE LIABILITY AND BUYERS EXCLUSIVE REMEDY FOR SOFTWARE AND EQUIPMENT COVERED BY THIS WARRANTY SHALL BE, AT THE SELLERS OPTION, REPAIR, REPLACEMENT OR A REFUND OF THE PRICE PAID BY THE BUYER.

THE WARRANTIES SET FORTH HEREIN ARE THE ONLY WARRANTIES, ORAL OR WRITTEN, MADE BY SELLER AND ARE IN LIEU OF AND REPLACE ALL OTHER WARRANTIES, EXPRESS OR IMPLIED, INCLUDING THE WARRANTY OF MERCHANTABILITY AND THE WARRANTY OF FITNESS FOR A PARTICULAR PURPOSE.

#### **RETURNS**

Equipment returned in new and unused condition in the original containers within 60 days will be subject to a restocking charge of 20%. Contact Teltone Repair Order Entry for a Material Return Authorization (MRA) number. Unauthorized returns will be subject to a \$50.00 surcharge and may be delayed due to the extra processing required.

#### INSPECTION

Seller may inspect any of the equipment furnished hereunder at any time during the warranty period. For specific product warranty periods refer to product price sheets.

# **Customer Information**

Teltone's experienced Product Support engineers are available for assistance in meeting your application needs.

Teltone cannot assume responsibility for use of any circuitry herein described other than circuitry entirely embodied in a Teltone proprietary product. No other circuit patent licenses are implied. Teltone reserves the right to change, without notice, any circuitry or specifications.

Prices and technical data are subject to change without notice.

**Teltone Corporation**

10801-120th Avenue NE Kirkland, WA 98033 Phone: 1-800-426-3926 or

206-827-9626 Fax: 206-827-6050 TWX: 910-449-2862 **Teltone Limited**

3375-14th Avenue Markham, Ontario L3R 2L6

Canada

Phone: 416-475-0837 Fax: 416-474-9151

Envoy User Name: TTL.HQ

Teltone is a registered trademark of Teltone Corporation. Touch-Tone is a registered trademark of AT&T. Copyright © 1990 Teltone Corporation. Printed in U.S.A.

# Section 2

# Selection Guides

# DTMF RECEIVERS AND TRANSMITTERS

|                            | M-957-01<br>(page 3-1) | M-957-02<br>(page 3-9) | M-8870<br>(page 3-17) | M-8880<br>(page 3-25) | M-8888<br>(page 3-37) |

|----------------------------|------------------------|------------------------|-----------------------|-----------------------|-----------------------|

| PACKAGE                    |                        |                        |                       |                       |                       |

| Monolithic IC              | •                      | •                      | •                     | •                     | •                     |

| Pin count                  | 22                     | 22                     | 18                    | 20                    | 20                    |

| CERDIP                     | ~ •                    | •                      | •                     | •                     | •                     |

| Plastic                    | •                      | •                      | •                     | •                     | •                     |

| CMOS technology            | •                      | •                      | •                     | •                     | •                     |

| OPERATION                  |                        |                        |                       |                       |                       |

| 12 V                       | •                      |                        |                       |                       |                       |

| 5 V                        | •                      | •                      | •                     | •                     | •                     |

| DTMF in                    | •                      | •                      | •                     | •                     | •                     |

| DTMF out                   |                        |                        |                       | •                     | •                     |

| Dial tone immune           | •                      | •                      | •                     | •                     | •                     |

| Call progress out          |                        |                        |                       | •                     | •                     |

| INPUT                      |                        |                        |                       |                       |                       |

| Differential AC            |                        |                        | •                     | •                     | •                     |

| Single-Ended AC            | •                      | •                      |                       |                       |                       |

| Adjustable receiver timing |                        |                        | •                     | •                     | •                     |

| OUTPUT                     |                        |                        |                       |                       |                       |

| Binary                     | •                      | •                      | •                     | •                     | •                     |

| Binary code 2-of-8         | •                      | •                      |                       |                       |                       |

| Tone                       |                        |                        |                       | •                     | •                     |

# CALL PROGRESS TONE RECEIVERS AND TRANSMITTERS

|                                    | M-980<br>(page 4-1) | M-981<br>(page 4-7) | M-982<br>(page 4-11) | M-984<br>(page 4-15) | M-991<br>(page 4-19) |

|------------------------------------|---------------------|---------------------|----------------------|----------------------|----------------------|

| PACKAGE                            |                     |                     |                      |                      |                      |

| Monolithic IC                      | •                   | •                   | •                    | •                    | •                    |

| Pin count                          | 8                   | 22                  | 22                   | 14                   | 14                   |

| CMOS                               | •                   | •                   | •                    | •                    | •                    |

| CERDIP                             | •                   |                     |                      | •                    | •                    |

| Plastic                            | •                   | •                   | •                    | •                    | •                    |

| OPERATION                          |                     |                     |                      |                      |                      |

| 5 V                                | •                   | •                   | •                    | •                    | •                    |

| Special Information Tones (S.I.T.) |                     |                     |                      | •                    |                      |

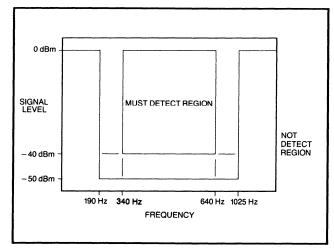

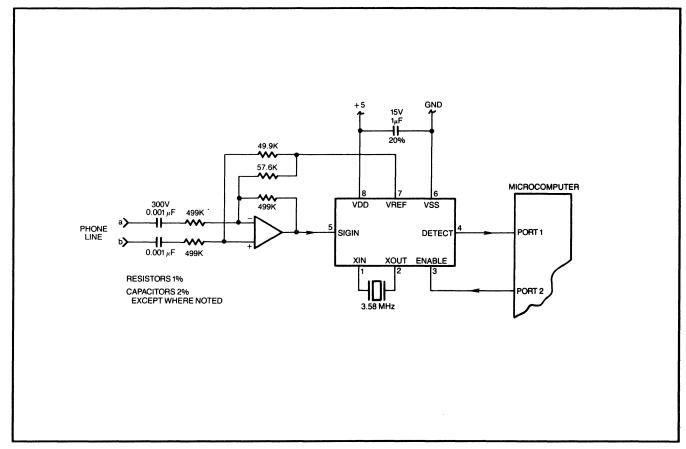

| Discriminators (Hz)                | 1                   | 4                   | 4                    | 4                    |                      |

| Dynamic range (dB)                 | 40                  | 30                  | 38                   | 30                   |                      |

| Call progress tones                | •                   | •                   | •                    | •                    | •                    |

| INPUT                              |                     |                     |                      |                      |                      |

| Single-ended AC                    | •                   | •                   | •                    | •                    |                      |

| Binary                             |                     |                     |                      |                      | •                    |

| OUTPUT                             |                     |                     |                      |                      |                      |

| Logic                              | •                   |                     |                      |                      |                      |

| 1-of-4                             |                     |                     |                      | •                    |                      |

| Tone                               |                     |                     |                      |                      | •                    |

| Any of 4                           |                     | •                   | •                    |                      |                      |

# MF RECEIVERS AND TRANSMITTERS

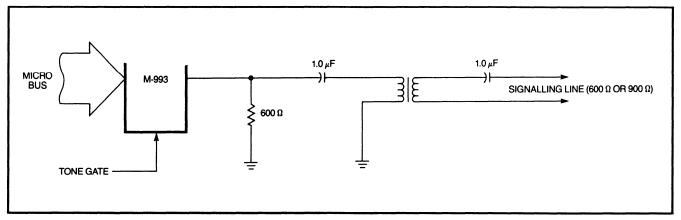

|                   | M-986-1R1<br>(page 5-1) | M-986-2R1<br>(page 5-1) | M-986-1R2<br>(page 5-3) | M-986-2R2<br>(page 5-3) | M-993<br>(page 5-15) |

|-------------------|-------------------------|-------------------------|-------------------------|-------------------------|----------------------|

| PACKAGE           |                         |                         |                         |                         |                      |

| Monolithic IC     | •                       | •                       | •                       | •                       | •                    |

| Pin count         | 40                      | 40                      | 40                      | 40                      | 14                   |

| Coprocessor port  | •                       | •                       | •                       | •                       |                      |

| Ceramic           | •                       | •                       | •                       | •                       |                      |

| CERDIP            |                         |                         |                         |                         | •                    |

| Plastic           | TBA*                    | TBA                     | TBA                     | TBA                     | •                    |

| Flat pack         | TBA                     | TBA                     | TBA                     | TBA                     |                      |

| OPERATION         |                         |                         |                         |                         |                      |

| 5 V               | •                       | •                       | •                       | •                       | •                    |

| Single channel    | •                       |                         | •                       |                         | •                    |

| Dual channel      |                         | •                       |                         | •                       |                      |

| STANDARDS         |                         |                         |                         |                         |                      |

| CCITT R1          | •                       | •                       |                         |                         | •                    |

| CCITT R2          |                         |                         | •                       | •                       |                      |

| INPUT             |                         |                         |                         |                         |                      |

| A-law PCM digital |                         |                         | •                       | •                       |                      |

| μ-law PCM digital | •                       | •                       |                         |                         |                      |

| OUTPUT            |                         |                         |                         |                         |                      |

| Linear (analog)   |                         |                         |                         |                         | •                    |

| CCITT R1 MF tone  |                         |                         |                         |                         | •                    |

| A-law PCM digital |                         |                         | •                       | •                       |                      |

| μ-law PCM digital | •                       | •                       |                         |                         |                      |

| Tone              |                         |                         |                         |                         | •                    |

| DATA FORMAT       |                         |                         |                         |                         |                      |

| Binary            | •                       | •                       | •                       | •                       |                      |

| 2-of-6            | •                       | •                       | •                       | •                       |                      |

<sup>\*</sup>To be announced.

# DC SIGNAL SENSORS

|                                  | M-949-01<br>(page 6-1) | M-949-02<br>(page 6-3) | M-949-03<br>(page 6-5) | M-949-06<br>(page 6-7) | M-949-10<br>(page 6-9) | M-959<br>(page 6-11) |

|----------------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|----------------------|

| PACKAGE                          |                        |                        |                        |                        |                        |                      |

| Line sense relay (1 Form A)      | •                      | •                      | •                      | •                      | •                      |                      |

| Monolithic IC                    |                        |                        |                        |                        |                        | •                    |

| Pin count                        | 6                      | 6                      | 6                      | 6                      | 6                      | 14                   |

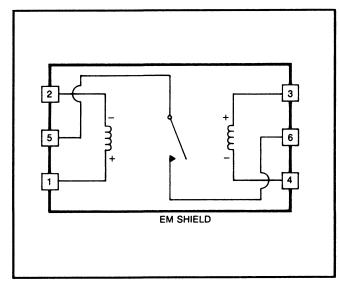

| Magnetic shielding               | •                      | •                      | •                      | •                      | •                      |                      |

| OPERATION                        |                        |                        |                        |                        |                        |                      |

| Line current                     | •                      | •                      | •                      | •                      | •                      |                      |

| 5 V                              |                        |                        |                        |                        |                        | •                    |

| Minimum pickup current (mA)      | 20                     | 15                     | 20                     | 15                     | 17.5                   |                      |

| Line current sense range (mA)    | 20-125                 | 15-170                 | 20-125                 | 15-170                 | 17.5-125               |                      |

| Max. closure time (ms)           | 1                      | 1                      | 1                      | 1                      | 1                      |                      |

| Typical longitudinal balance(dB) | 63                     | 70                     | 63                     | 70                     | 63                     |                      |

| Resistance (ohms/coil)           | 20                     | 20                     | 9                      | 9                      | 20                     |                      |

| Coil-to-contact isolation(VRMS)  | 1500                   | 3750                   | 1500                   | 2250                   | 1500                   |                      |

| STANDARDS                        |                        |                        |                        |                        |                        |                      |

| U.S. FCC Part 68                 | •                      |                        |                        |                        | •                      |                      |

| International (IEC/VDE)          |                        | •                      |                        |                        |                        |                      |

| Canadian (DOC/CSA)               |                        |                        | •                      | •                      |                        |                      |

| INPUT                            |                        |                        |                        |                        |                        |                      |

| DC logic                         | •                      | •                      | •                      | •                      | •                      | •                    |

| 10 pps pulse                     | •                      | •                      | •                      | •                      | •                      | •                    |

| 20 pps pulse                     | •                      | •                      | •                      | •                      | •                      | •                    |

| OUTPUT                           |                        |                        |                        |                        |                        |                      |

| Binary                           |                        |                        |                        |                        |                        | •                    |

| Relay contact                    | •                      | •                      | •                      | •                      | •                      |                      |

# **Section 3**

# DTMF Receivers and Transmitters

## M-957-01 DTMF RECEIVER

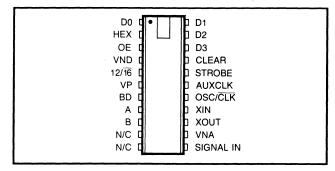

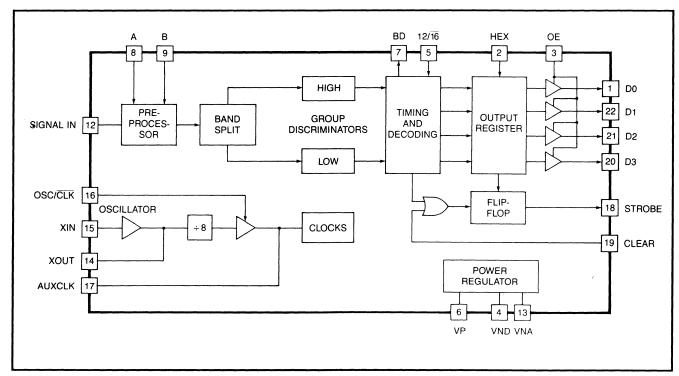

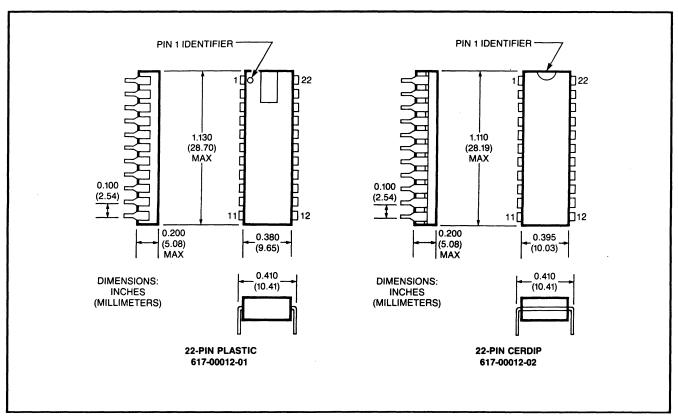

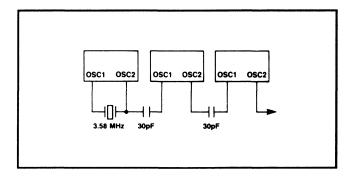

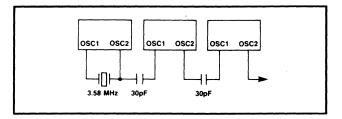

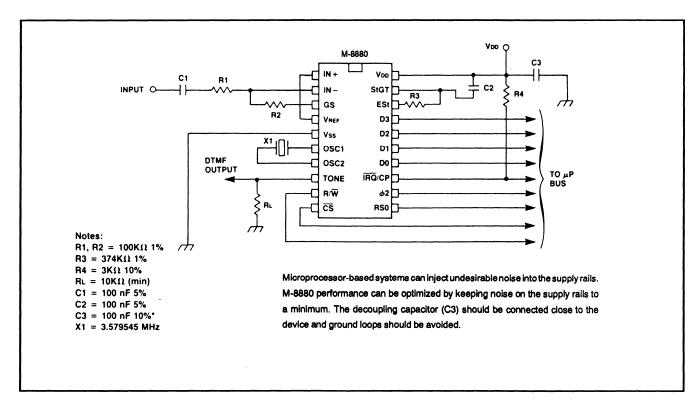

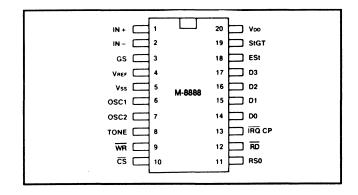

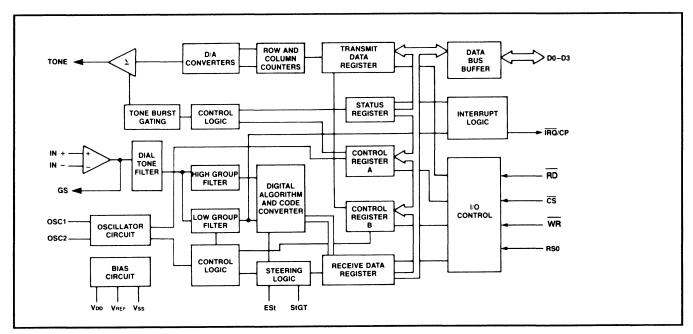

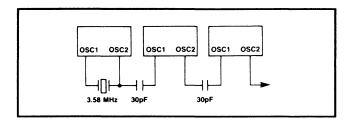

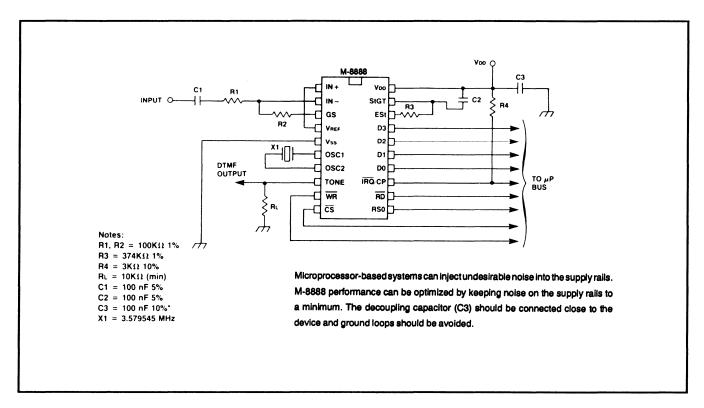

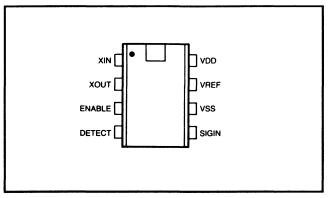

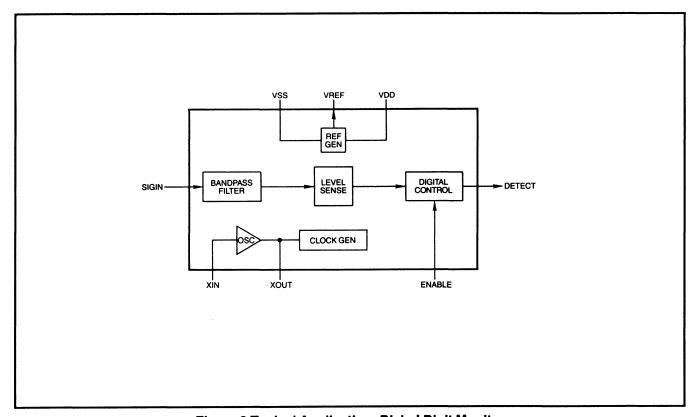

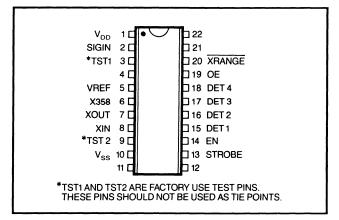

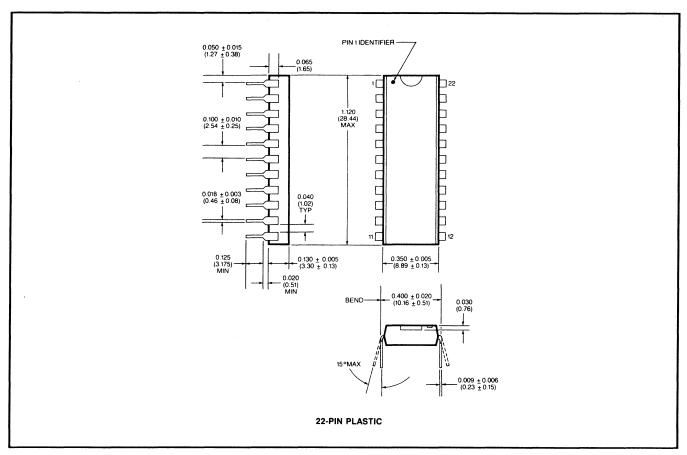

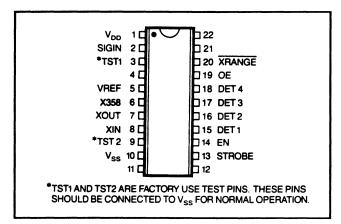

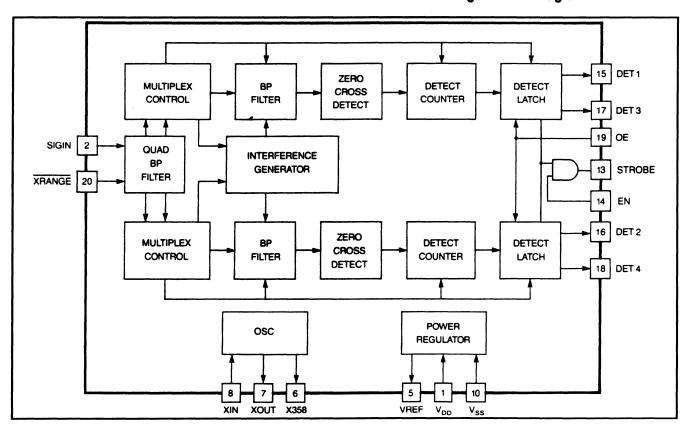

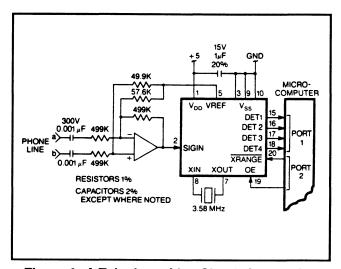

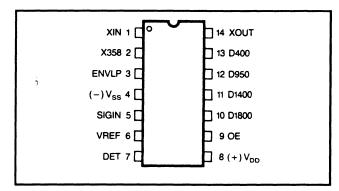

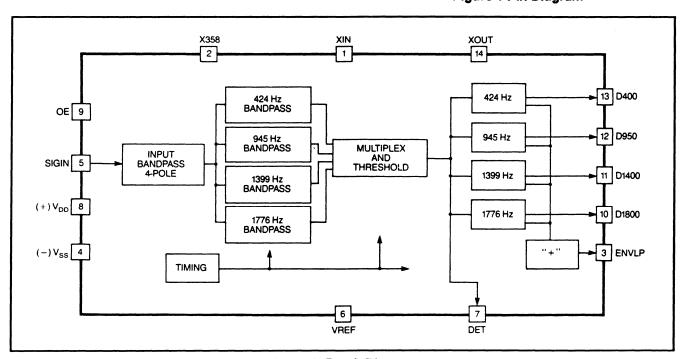

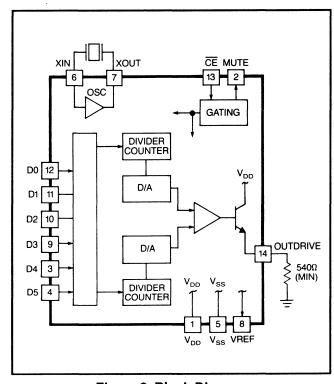

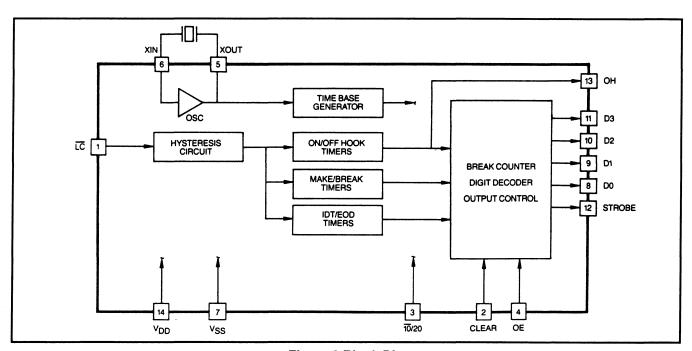

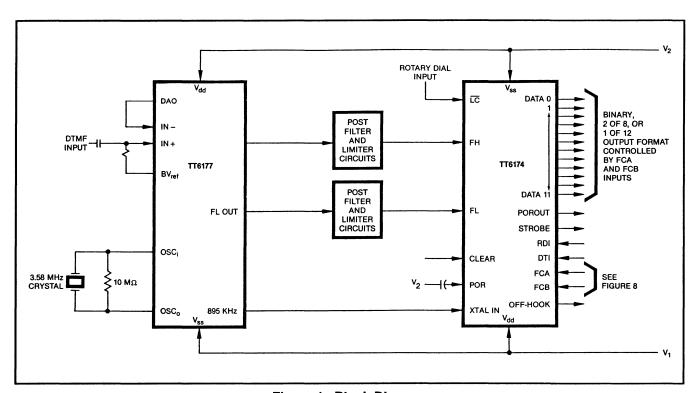

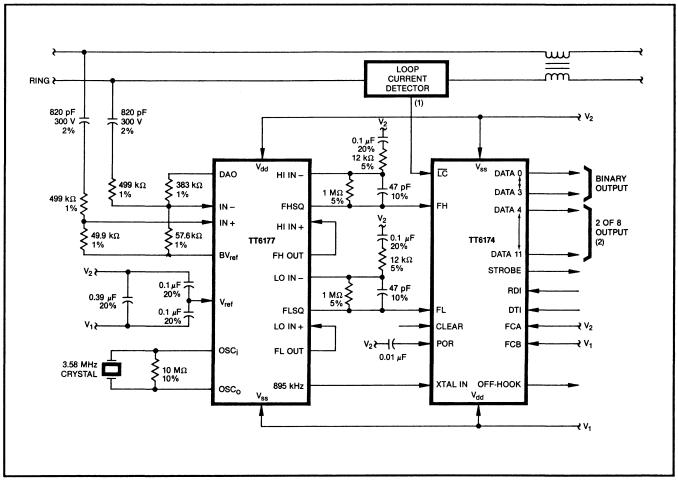

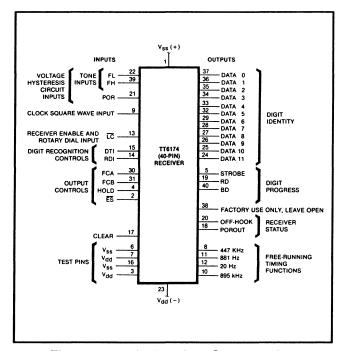

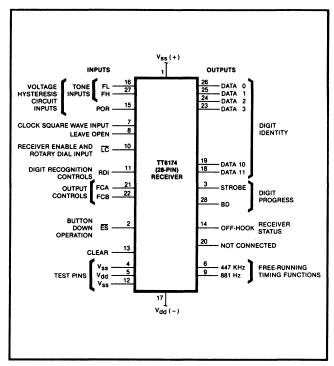

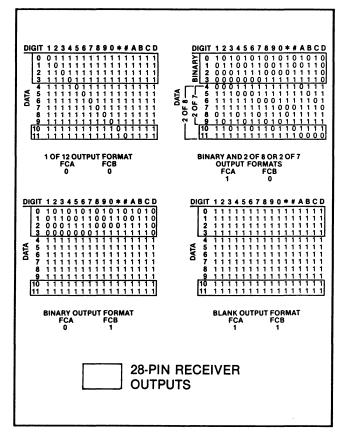

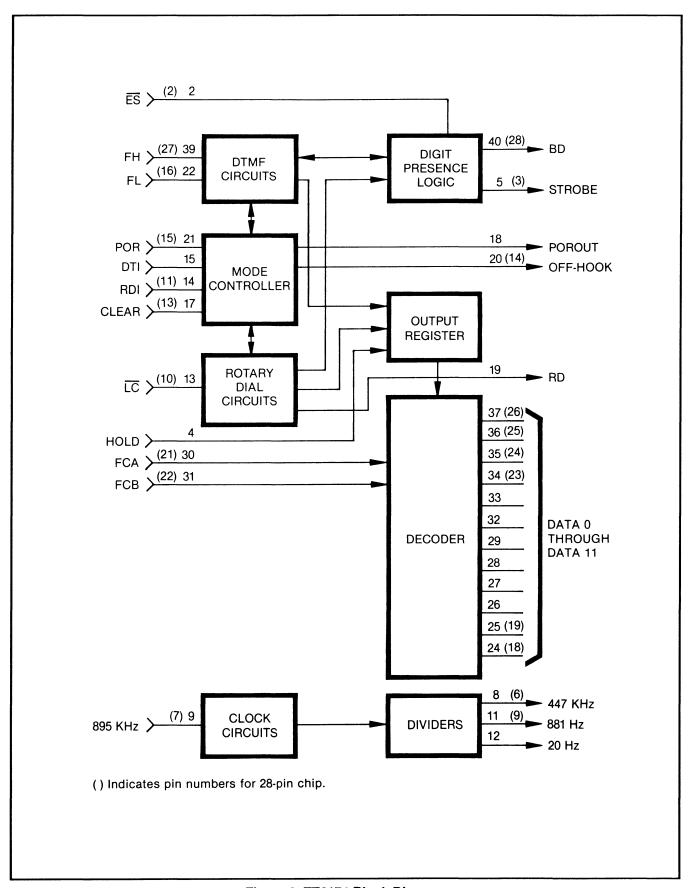

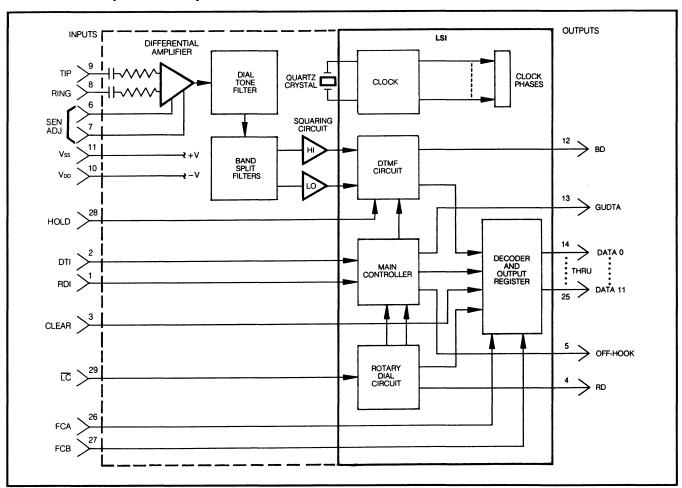

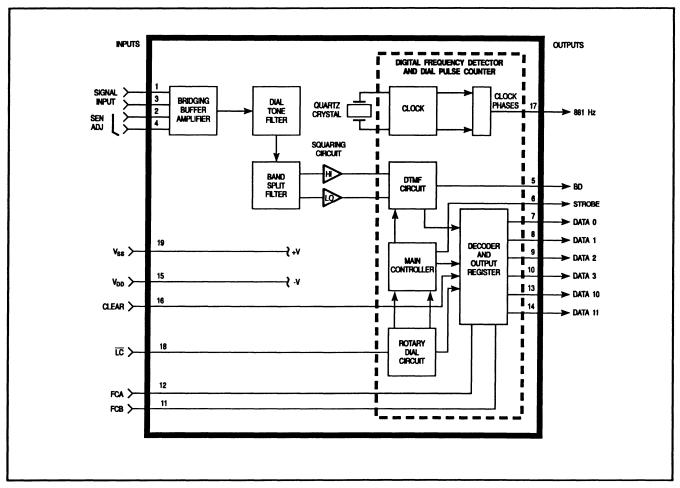

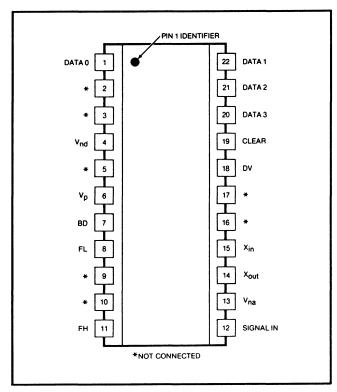

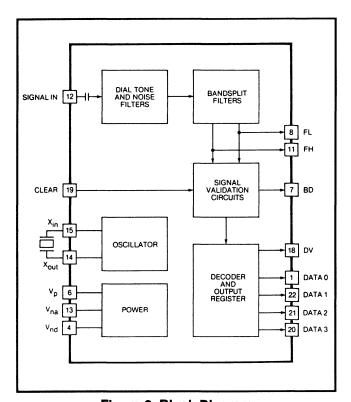

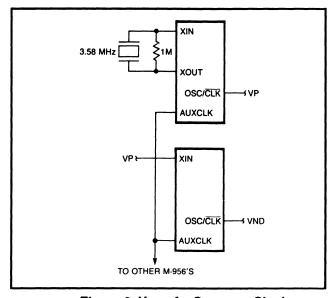

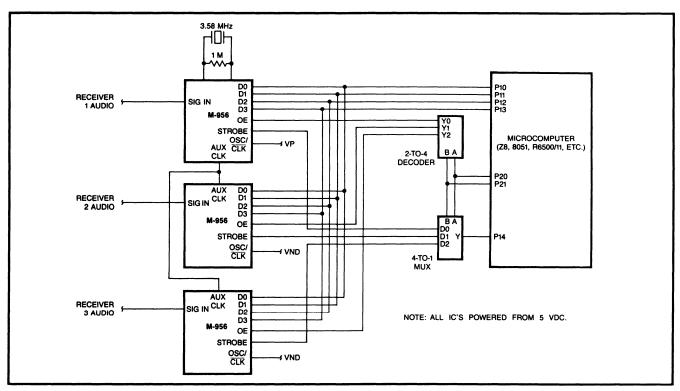

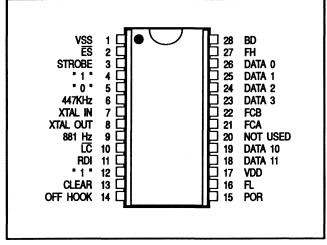

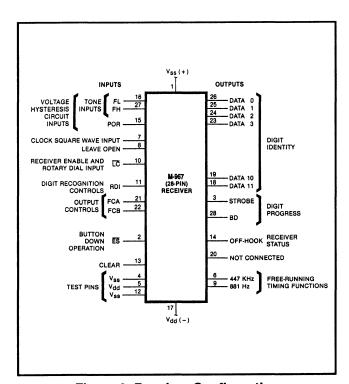

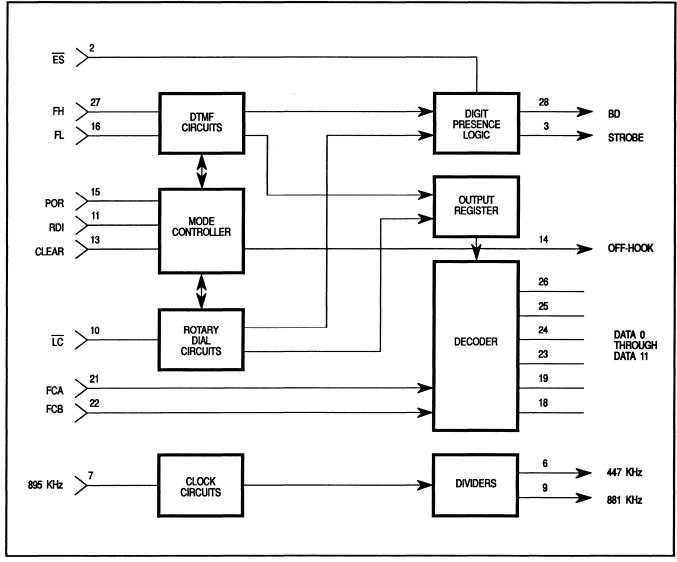

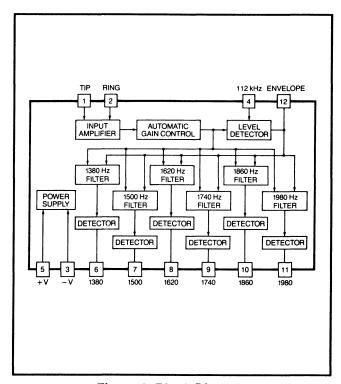

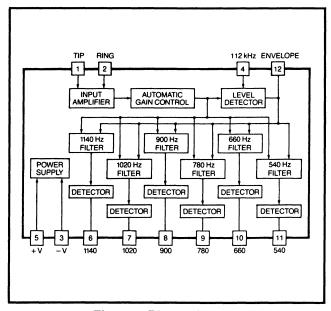

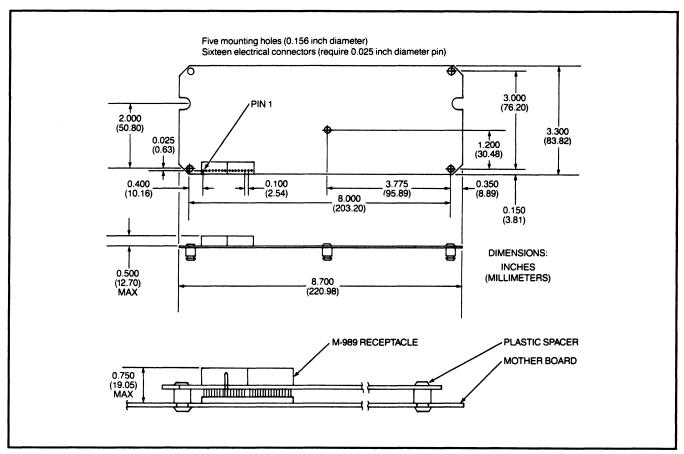

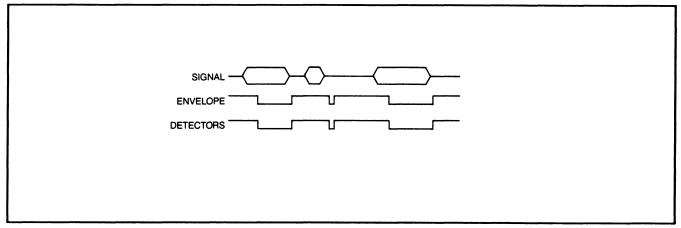

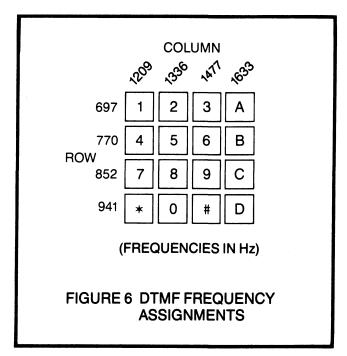

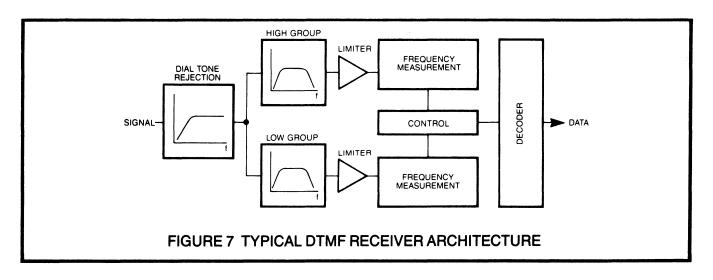

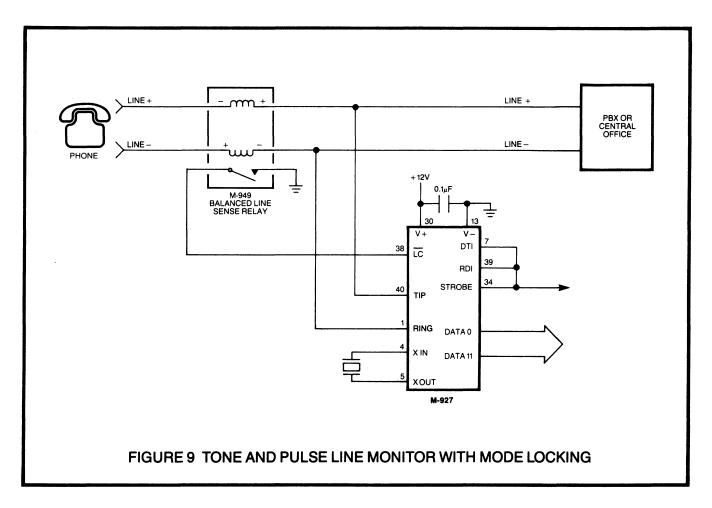

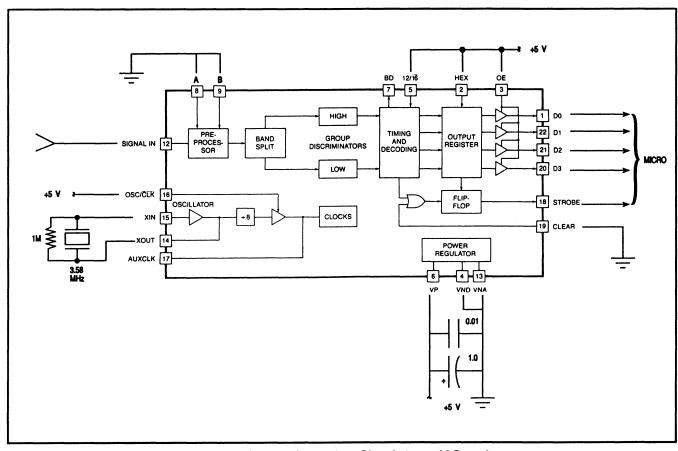

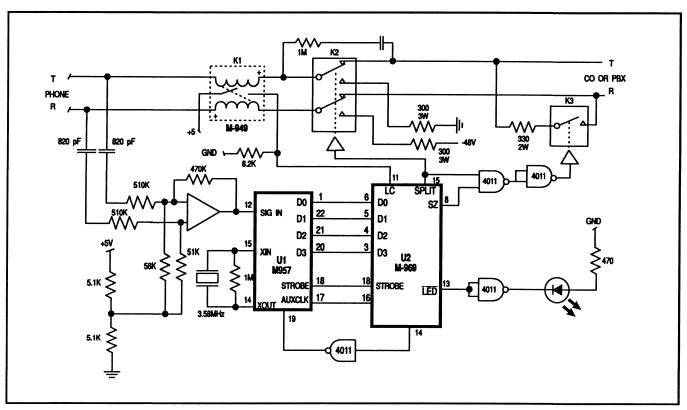

The Teltone M-957-01 (see Figure 1) combines switched-capacitor and digital frequency measuring techniques to decode Dual-Tone Multifrequency (DTMF) signals to four-bit binary data. Dial tone rejection and 60-Hz noise rejection filters are built in. Fabricated as a monolithic integrated circuit using low-power CMOS processing, the M-957-01 is packaged in a 22-pin DIP and operates from a wide 5-through-12-volt DC supply. An inexpensive 3.58-MHz television crystal and resistor are the only external components required. High system density may be achieved by using the clock output of one crystal-connected receiver to drive the time bases of additional receivers.

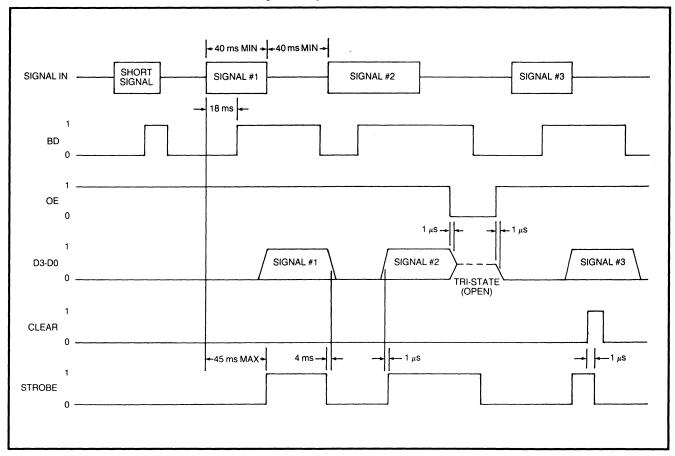

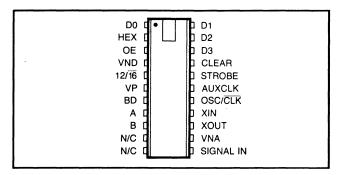

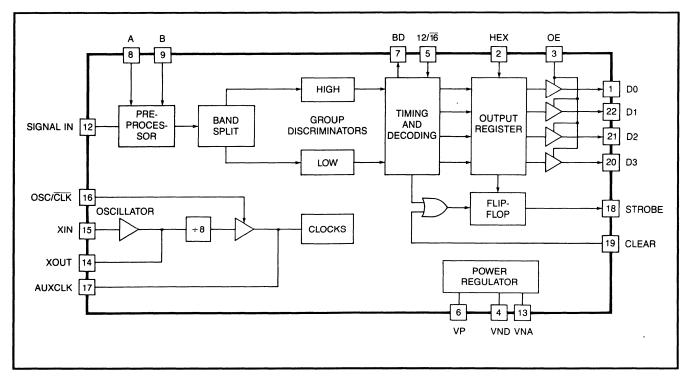

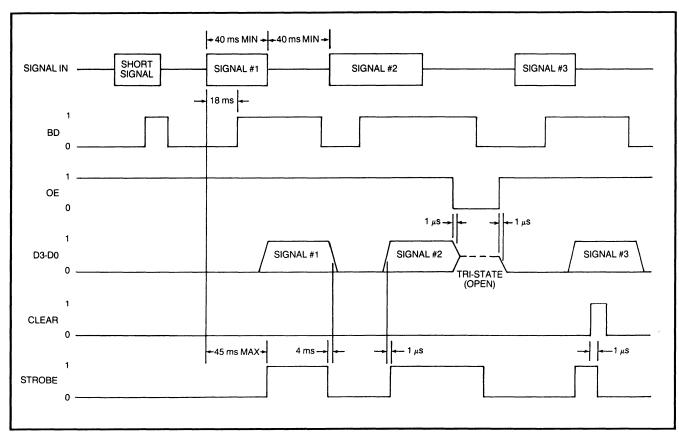

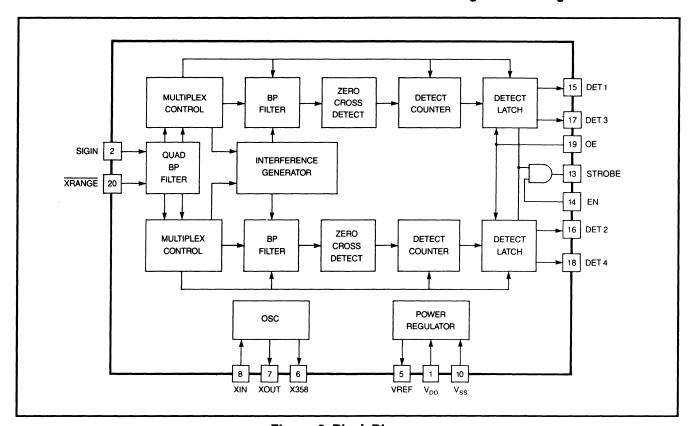

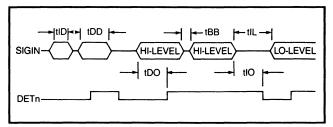

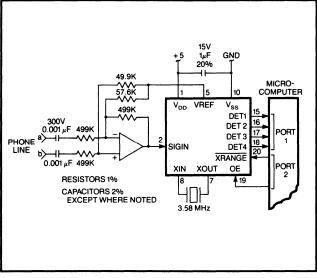

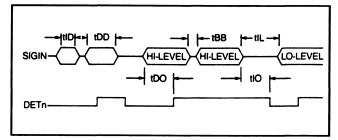

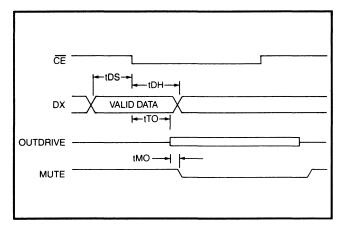

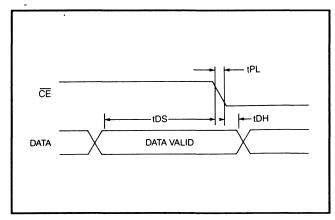

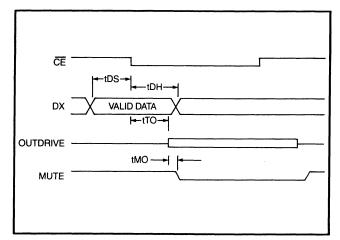

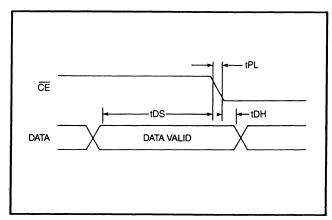

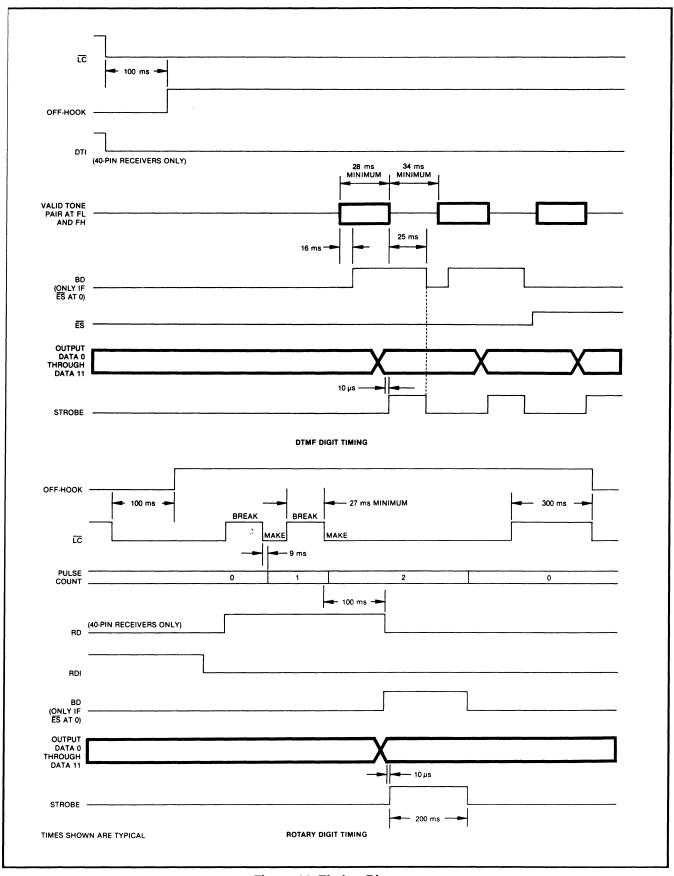

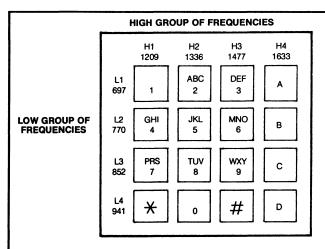

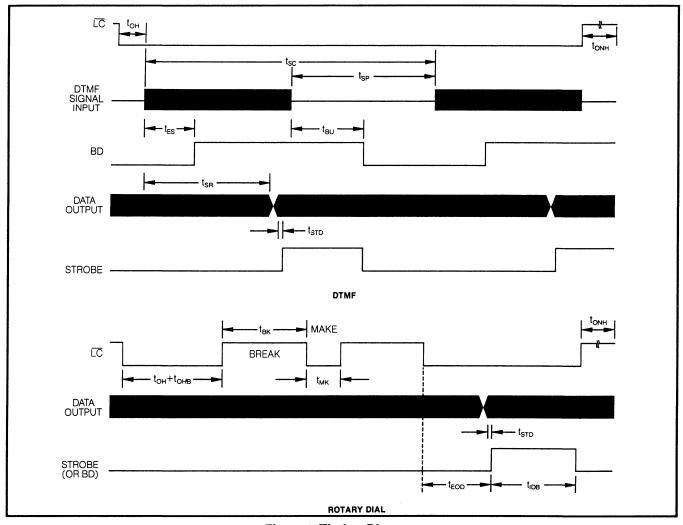

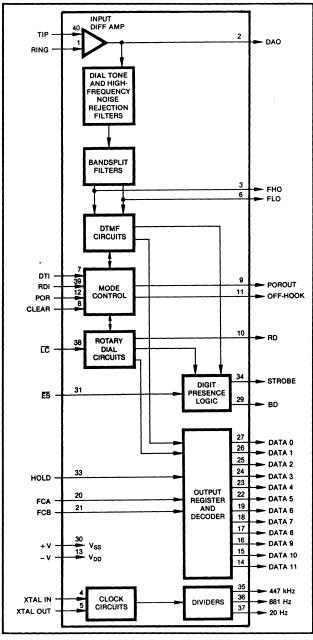

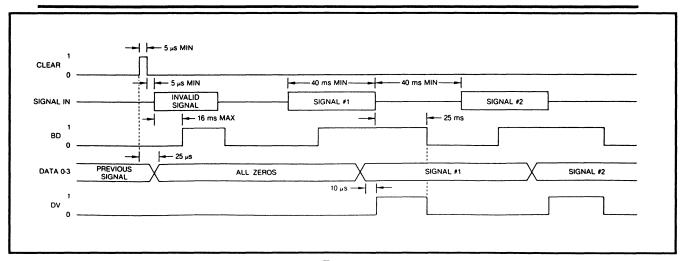

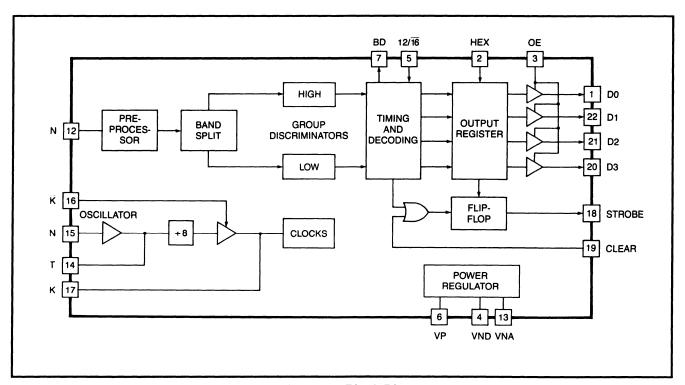

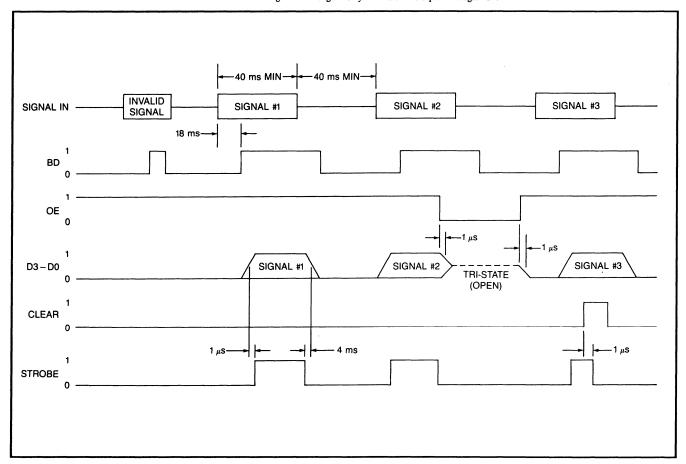

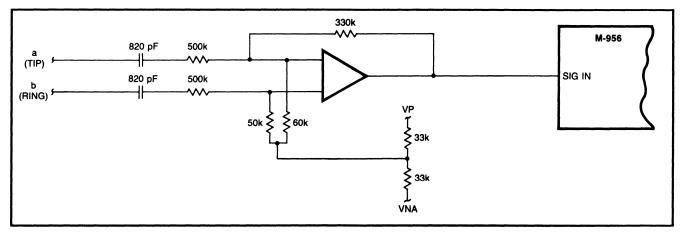

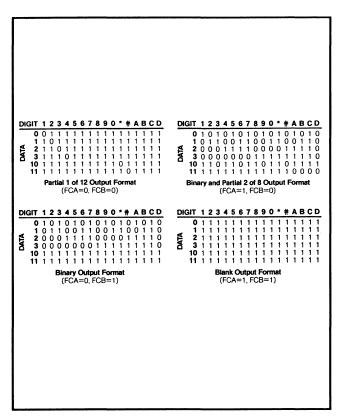

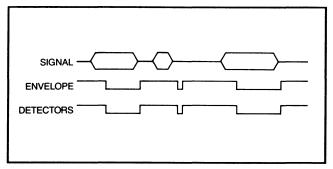

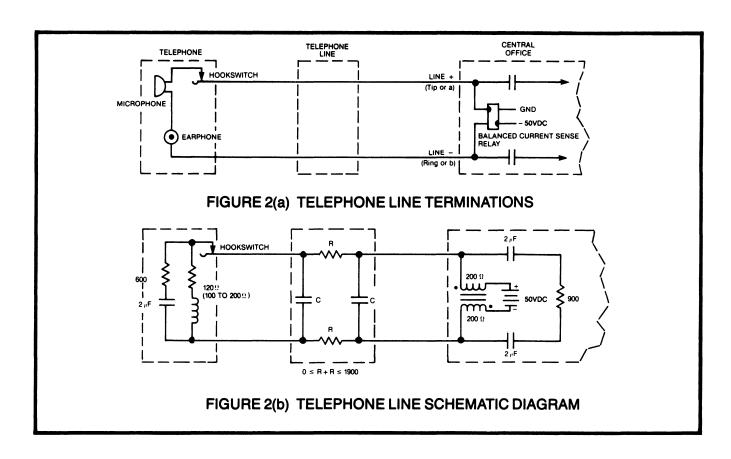

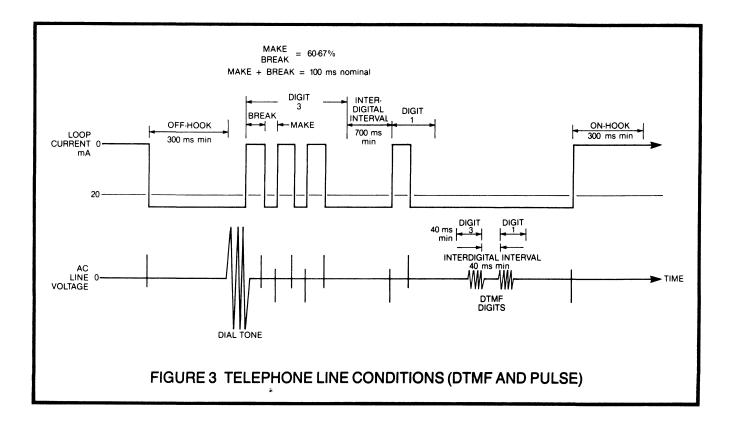

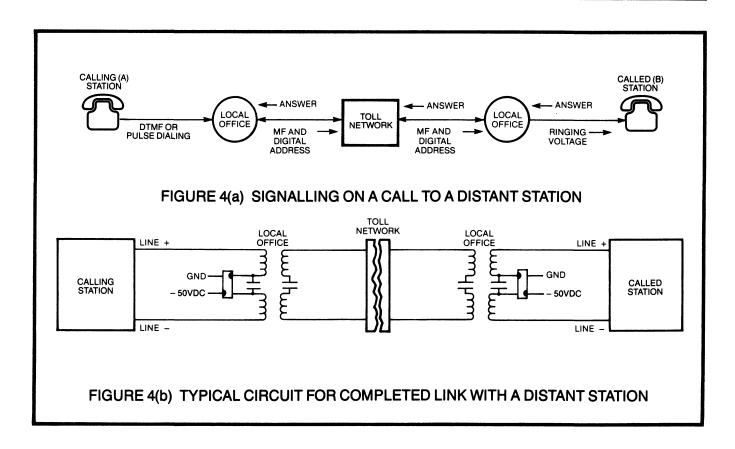

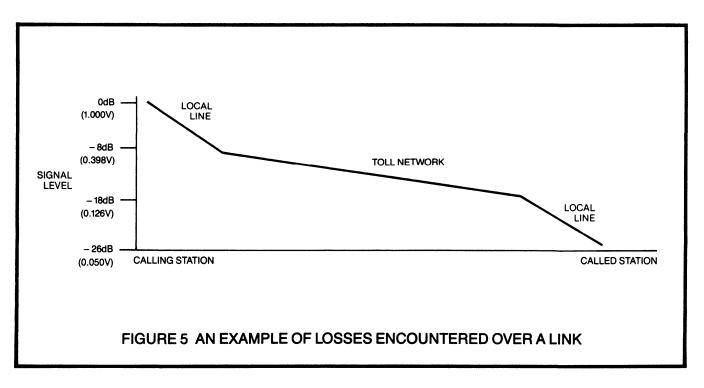

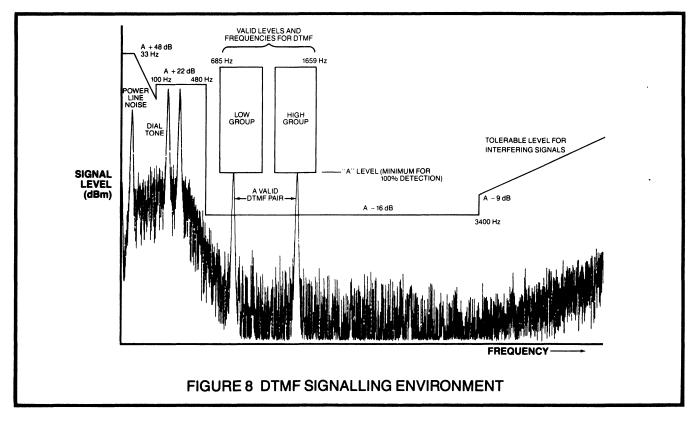

The SIGNAL IN input to the M-957 (see Figure 2) interfaces readily to telephone lines, radio receivers, tape players, and other DTMF signal sources. Inputs A and B control sensitivity to a maximum of -38 dBm at 5 V, while the 12/16 input determines the signals to be detected. The preprocessing stages of the M-957 filter out dial tone and noise, split the signal into its high- and low-frequency components, and hard-limit each component to provide automatic gain control. Four discriminators in each group then detect the individual tones. Postprocessing stages of the M-957 time the tone durations and store binary data for outputting as determined by the HEX input. The STROBE output is activated by the

presence of valid data in the output register and cleared by the detection of a valid end-of-signal pause or by the CLEAR input. An early signal presence indicator, BD, facilitates applications requiring tone blocking. The data outputs operate with simple logic circuits or microprocessors, and are three-state enabled to facilitate bus-oriented architectures.

#### **Features**

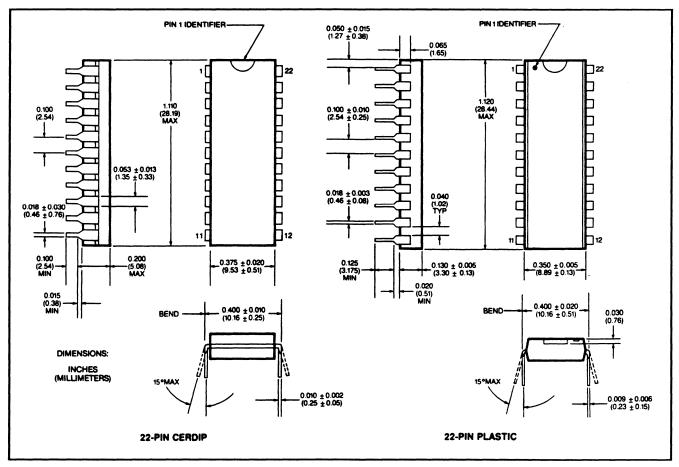

- Complete DTMF receiver in 22-pin DIP (plastic or CerDIP)

- Decodes all 16 DTMF digits

- Excellent dial tone and speech immunity

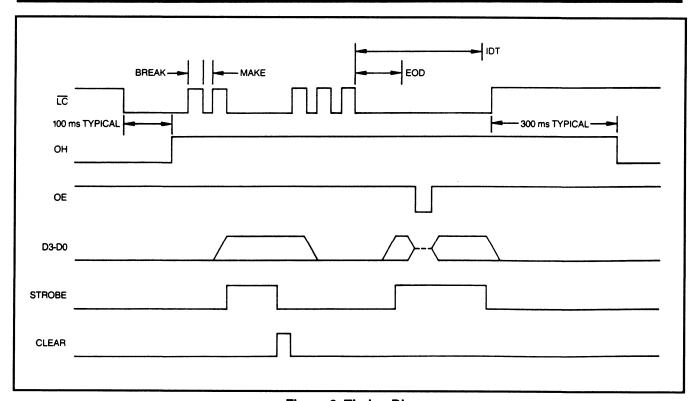

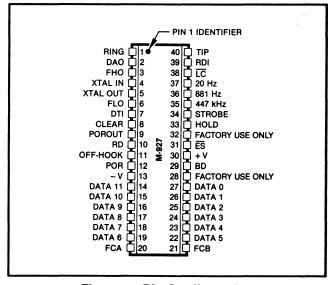

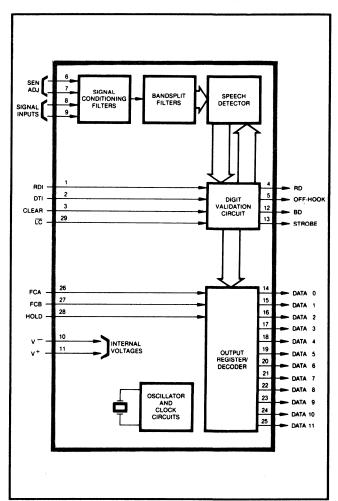

Figure 1 Pin Diagram

Figure 2 Block Diagram

- Meets telephone impulse noise immunity standards

- Digitally selectable sensitivity to -38 dBm

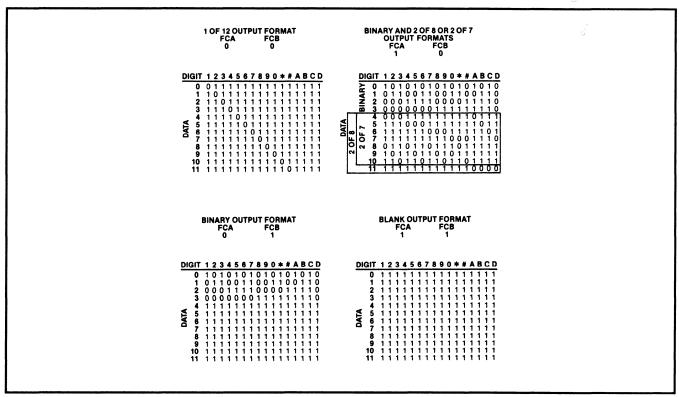

- Selectable 4-bit hexadecimal or binary coded 2 of 8 output

- Fabricated using low-power CMOS technology

- Operates on single DC supply

- Uses inexpensive 3.58-MHz crystal

- Three-state outputs

- 5- through 12-volt supply

#### **Applications**

- Central office products

- · PBX and key systems

- Radio telephones

- Remote control and monitoring devices

- Computer data entry systems

#### **Table 1 Pin Functions**

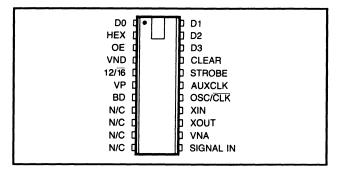

| Pin            | Function                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

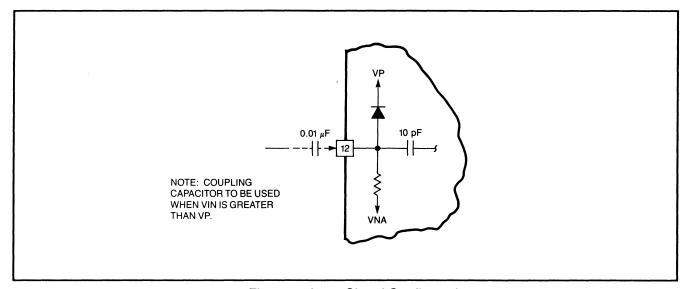

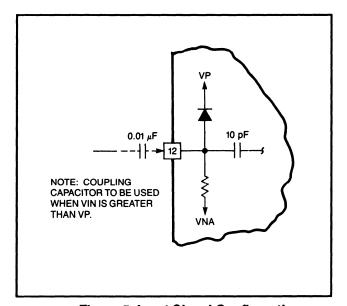

| SIGNAL IN      | DTMF input. Timings are shown in Figure 3. Internally biased so that the input signal may be AC coupled, SIGNAL IN also permits DC coupling as long as the input voltage does not exceed the positive supply. Proper coupling is shown in Figure 5. See Table 2 for the frequency pairs associated with each DTMF signal. |  |  |  |  |  |

| 12/16          | DTMF signal detection control. When 12/k is at logic "1", the M-957 detects the 12 most commonly used DTMF signals (1 through #). When 12/k is at logic "0", the M-957 detects all 16 DTMF signals (1 through D).                                                                                                         |  |  |  |  |  |

| A, B           | Binary DTMF signal sensitivity control inputs. A and B select the sensitivity of the SIGNAL IN input to a maximum of -31 dBm.                                                                                                                                                                                             |  |  |  |  |  |

| D3, D2, D1, D0 | Data outputs. When enabled by the OE input, the data outputs provide the code corresponding to the detected digit in the format programmed by the HEX pin. See Table 2. The data outputs become valid after a tone pair has been detected and are cleared when a valid pause is timed. Timings are shown in Figure 3.     |  |  |  |  |  |

| OE             | Output enable. When OE is at logic "1", the data outputs are in the CMOS push/pull state and represent the contents of the output register (see Figure 2). When OE is driven to logic "0", the data outputs are forced to the high-impedance or "third" state. Timings are shown in Figure 3.                             |  |  |  |  |  |

| нех            | Binary output format control. When HEX is at logic "1", the output of the M-957 is full, 4-bit binary. When HEX is at logic "0", the output is binary coded 2-of-8. Table 2 shows the output codes.                                                                                                                       |  |  |  |  |  |

| STROBE         | Valid data indication. STROBE goes to logic "1" after a valid tone pair is sensed and decoded at the data outputs. STROBE remains at logic "1" until a valid pause occurs or the CLEAR input is driven to logic "1", whichever is earlier. Timings are shown in Figure 3.                                                 |  |  |  |  |  |

| CLEAR .        | STROBE control. Driving CLEAR to logic "1" forces the STROBE output to logic "0". When CLEAR is at logic "0", STROBE is forced to logic "0" only when a valid pause is detected. Tie to VNA or VND when not used.                                                                                                         |  |  |  |  |  |

| BD             | Early signal presence output. BD indicates that a possible signal has been detected and is being validated. As shown in Figure 3, BD precedes STROBE and the data outputs.                                                                                                                                                |  |  |  |  |  |

| XIN, XOUT      | Crystal connections. When an auxiliary clock is used, XIN should be tied to logic "1". See Figure 6.                                                                                                                                                                                                                      |  |  |  |  |  |

| OSC/CLK        | Time base control. When OSC/CLK is at logic "1", the output of the M-957's internal oscillator is selected as the time base. When OSC/CLK is at logic "0" and XIN is at logic "1", the AUXCLK input is selected as the time base.                                                                                         |  |  |  |  |  |

| AUXCLK         | Auxiliary clock input. When OSC/CLK is at logic "0" and XIN is at logic "1", the AUXCLK input is selected as the M-957's time base. The auxiliary input must be 3.58 MHz divided by 8 for the M-957 to operate to specifications. If unused, AUXCLK should be left open.                                                  |  |  |  |  |  |

| VNA, VND       | Negative analog and digital power supply connections. Separated on the chip for greater system flexibility, VNA and VND should be at equal potential.                                                                                                                                                                     |  |  |  |  |  |

| VP             | Positive power supply connection.                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| N/C            | Not connected. These pins have no internal connection and may be left floating.                                                                                                                                                                                                                                           |  |  |  |  |  |

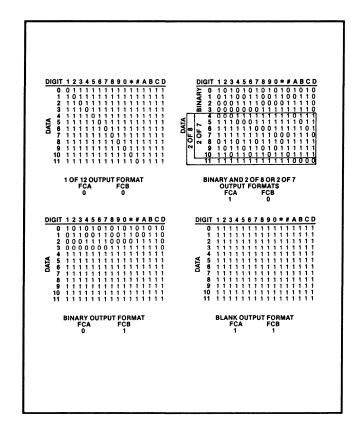

Table 2 DTMF to Binary Decoding

| LOW-<br>FREQUENCY<br>COMPONENT | HIGH-<br>FREQUENCY<br>COMPONENT                                                                              | HEX<br>OUTPUT<br>FORMAT                                                                                                                             | 2-OF-8<br>OUTPUT<br>FORMAT                                                                                                                                                                                                                                                                            |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| (Hz)                           | (Hz)                                                                                                         | 3 2 1 0                                                                                                                                             | 3 2 1 0                                                                                                                                                                                                                                                                                               |  |

|                                |                                                                                                              | 0001                                                                                                                                                |                                                                                                                                                                                                                                                                                                       |  |

|                                |                                                                                                              |                                                                                                                                                     | 0000                                                                                                                                                                                                                                                                                                  |  |

|                                |                                                                                                              |                                                                                                                                                     | 0001                                                                                                                                                                                                                                                                                                  |  |

|                                |                                                                                                              |                                                                                                                                                     | 0010                                                                                                                                                                                                                                                                                                  |  |

| 770                            | 1209                                                                                                         | 0100                                                                                                                                                | 0100                                                                                                                                                                                                                                                                                                  |  |

| 770                            | 1336                                                                                                         | 0101                                                                                                                                                | 0101                                                                                                                                                                                                                                                                                                  |  |

|                                |                                                                                                              |                                                                                                                                                     | 0110                                                                                                                                                                                                                                                                                                  |  |

|                                |                                                                                                              |                                                                                                                                                     | 1000                                                                                                                                                                                                                                                                                                  |  |

|                                |                                                                                                              |                                                                                                                                                     | 1001                                                                                                                                                                                                                                                                                                  |  |

| 032                            | 1550                                                                                                         | 1000                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                     |  |

| 852                            | 1477                                                                                                         | 1001                                                                                                                                                | 1010                                                                                                                                                                                                                                                                                                  |  |

| 941                            |                                                                                                              | 1010                                                                                                                                                | 1101                                                                                                                                                                                                                                                                                                  |  |

| 941                            | 1209                                                                                                         | 1011                                                                                                                                                | 1100                                                                                                                                                                                                                                                                                                  |  |

|                                | 1477                                                                                                         | 1100                                                                                                                                                | 1110                                                                                                                                                                                                                                                                                                  |  |

|                                |                                                                                                              |                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                     |  |

| 697                            | 1633                                                                                                         | 1101                                                                                                                                                | 0011                                                                                                                                                                                                                                                                                                  |  |

| 770                            | 1633                                                                                                         | 1110                                                                                                                                                | 0111                                                                                                                                                                                                                                                                                                  |  |

| 852                            | 1633                                                                                                         | 1111                                                                                                                                                | 1011                                                                                                                                                                                                                                                                                                  |  |

| 941                            | 1633                                                                                                         | 0000                                                                                                                                                | 1111                                                                                                                                                                                                                                                                                                  |  |

|                                | 697<br>697<br>697<br>770<br>770<br>770<br>852<br>852<br>852<br>941<br>941<br>941<br>941<br>697<br>770<br>852 | (Hz) (Hz)  697 1209 697 1336 697 1477 770 1209  770 1336 770 1477 852 1209 852 1336  852 1477 941 1336 941 1209 941 1477 697 1633 770 1633 852 1633 | (Hz) (Hz) 3 2 1 0  697 1209 0 0 0 1 697 1336 0 0 1 0 697 1477 0 0 1 1 770 1209 0 1 0 0  770 1336 0 1 0 1 770 1477 0 1 1 0 852 1209 0 1 1 1 852 1209 0 1 1 1 852 1336 1 0 0 0  852 1477 1 0 0 1 941 1336 1 0 1 0 941 1209 1 0 1 1 941 1477 1 1 0 0  697 1633 1 1 0 1 770 1633 1 1 1 0 852 1633 1 1 1 1 |  |

Note: The M-957 detects signals A through D only when the 12/16 input is at logic "0".

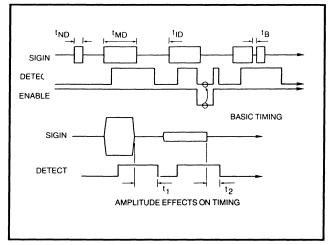

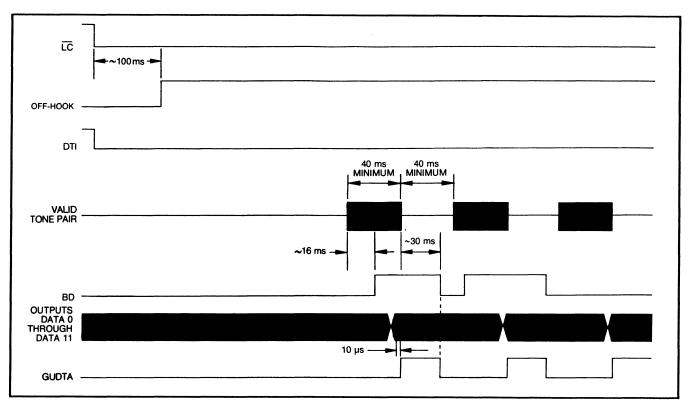

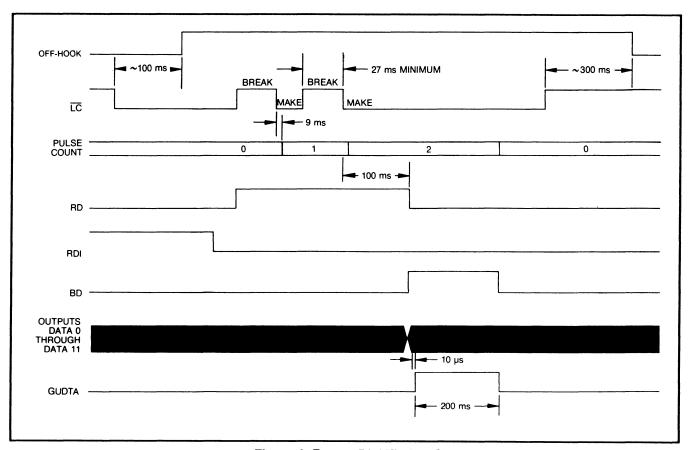

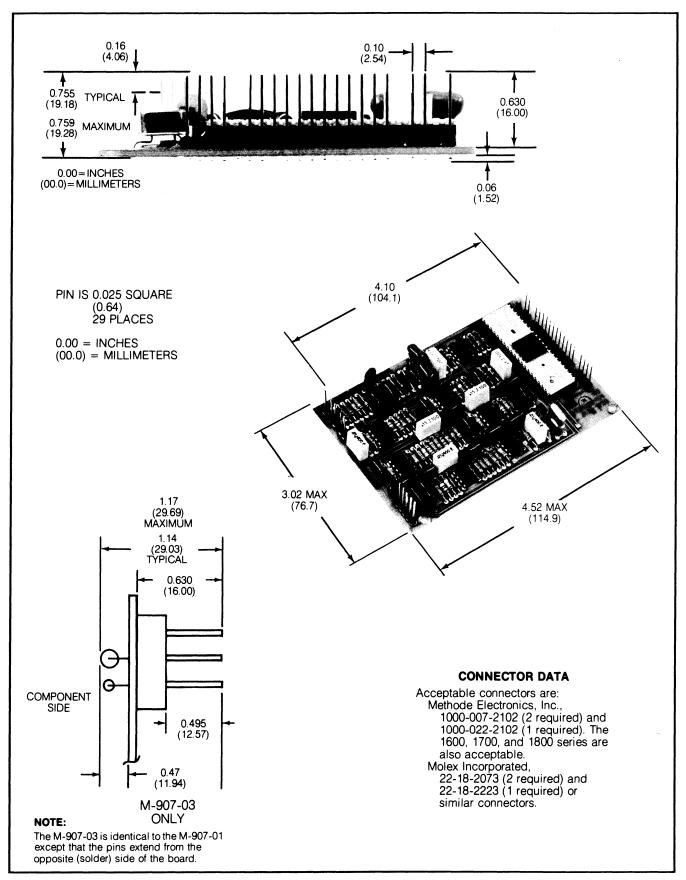

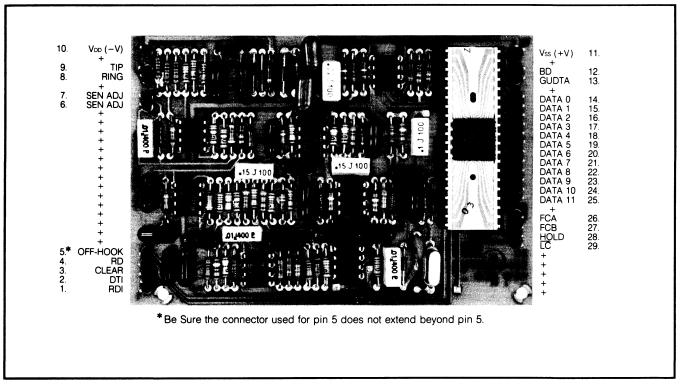

Figure 3 Timing Diagram

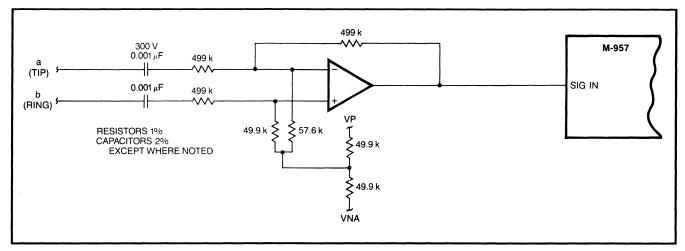

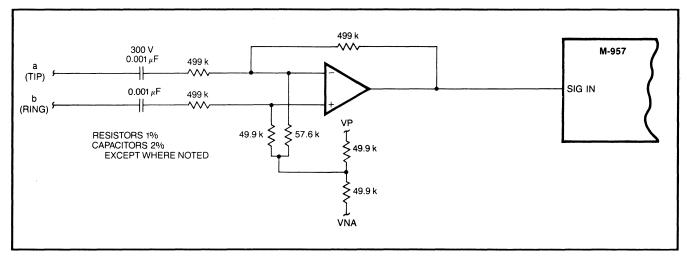

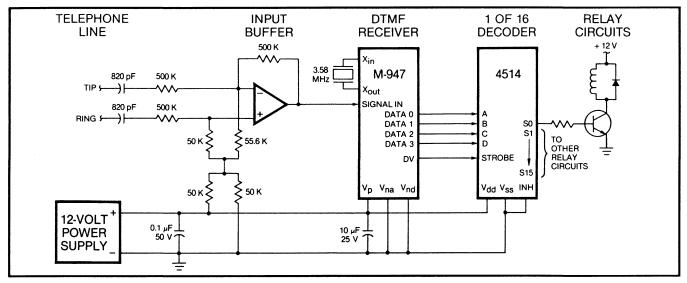

Figure 4 Telephone Line Differential Input Interface

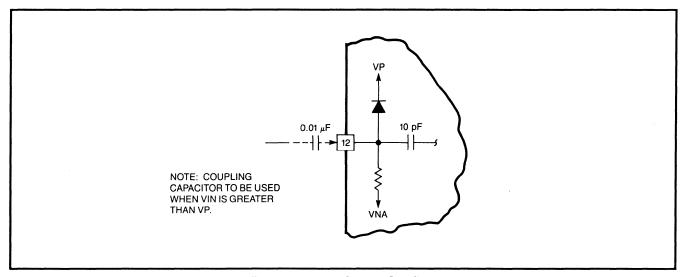

Figure 5 Input Signal Configuration

#### Table 3 Absolute Maximum Ratings (Note 1)

| DC Supply Voltage (Note 2)          |

|-------------------------------------|

| Voltage on SIGNAL IN                |

| Voltage on Any Pin Except SIGNAL IN |

| Storage Temperature Range           |

| Operating Temperature Range         |

| Lead Soldering Temperature          |

| Power Dissipation                   |

#### Notes:

- 1. Exceeding these ratings may permanently damage the M-957.

- 2. VP referenced to VND. VND should be at equal potential to VNA. VND/VNA may be at ground.

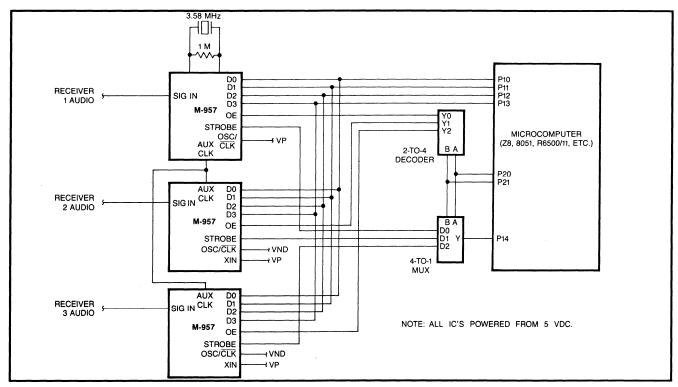

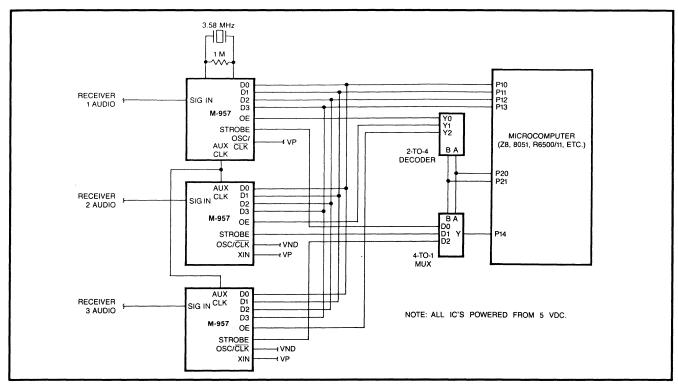

Figure 6 Multiple Receiver/Microprocessor Interface

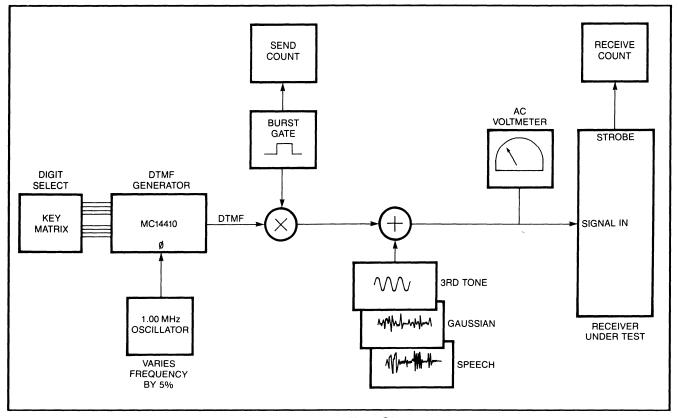

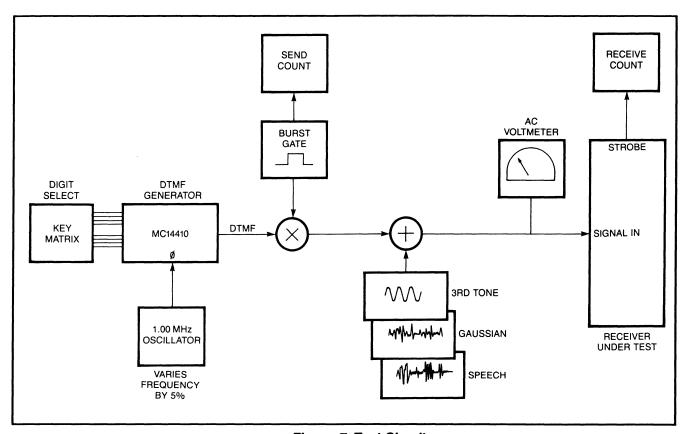

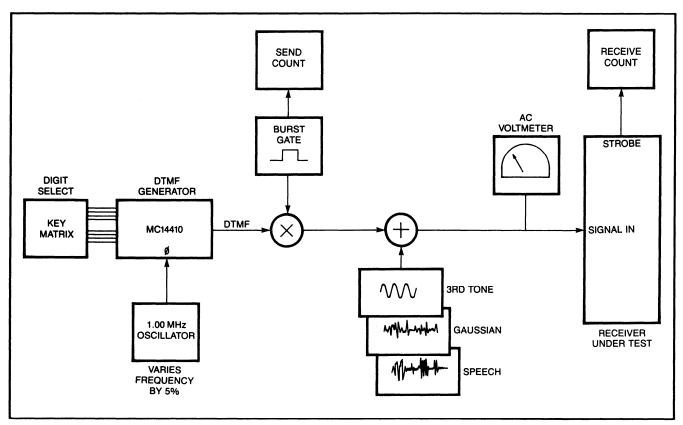

Figure 7 Test Circuit

Table 4 Specifications

|                       | Parameter                                    | Conditions                          | Min        | Тур       | Max         | Units      | Notes  |

|-----------------------|----------------------------------------------|-------------------------------------|------------|-----------|-------------|------------|--------|

| SIGNAL IN Input       | Signal Level (per tone)                      | VP = 12V                            |            |           |             |            |        |

| Requirements          | <b>g</b> ,                                   | A = 0, B = 0                        | -24        | _         | +6          | dBm        | 1      |

|                       |                                              | A = 1, B = 0                        | -27        | -         | +3          | dBm        | 1      |

|                       |                                              | A = 0, B = 1<br>A = 1, B = 1        | -30        | -32       | 0           | dBm<br>dBm | 1 1    |

|                       |                                              | VP=5V                               | -          | - 32      | _           | ubiii      | '      |

|                       |                                              | A = 0, B = 0                        | -32        | _         | -2          | dBm        | 1      |

|                       |                                              | A=1, B=0                            | -35        | -         | -5          | dBm        | 1      |

|                       |                                              | A = 0, B = 1                        | -38        |           | -8          | dBm        | !      |

|                       |                                              | A = 1, B = 1                        | _          | -40       | -           | dBm        | 1      |

|                       | Signal Duration                              | -                                   | 40         | _         | _           | ms         |        |

|                       | Interval Between Signals                     | _                                   | 40         | -         | _           | ms         |        |

|                       | Signal Present Without Detection             | _                                   | -          | -         | 20          | ms         |        |

|                       | Interruption of Signal Without Redetection   | _                                   | _          |           | 20          | ms         |        |

|                       | Signal Frequency Deviation With Detection    | _                                   | _          | ±2.5%     | ±(1.5%+2)   | Hz         |        |

|                       | Signal Frequency Deviation Without Detection | _                                   | ± 3.5%     | ±3.0%     | _           | Hz         |        |

|                       | Twist                                        | _                                   | _          | _         | ± 10        | dB         | 2      |

|                       | Gaussian Noise                               |                                     | _          | 12        | A-7         | dB         | 3      |

|                       | Dial Tone Level                              |                                     |            |           |             |            |        |

|                       | (per tone, F≤480 Hz)                         | _                                   | _          | _         | A + 22      | dB         | 4      |

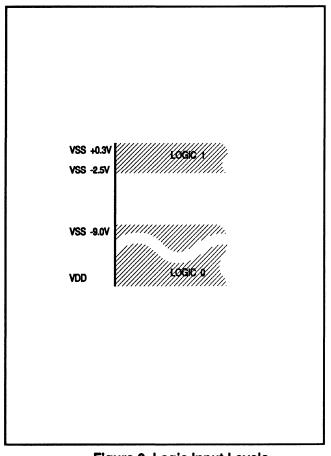

| Digital Input         | Logic 0 Voltage                              | VP = 12V                            | 0          | _         | 3.6         | v          | 5      |

| Requirements          |                                              | VP=5V                               | 0          | _         | 1.5         | V          | 5      |

|                       | Logic 1 Voltage                              | VP = 12V $VP = 5V$                  | 8.4<br>3.5 | _         | 12.0<br>5.0 | V<br>V     | 5<br>5 |

| Digital Output        | Logic 0 Voltage                              | $VP = 12V, I_O = 1.0 \text{ mA}$    | 0          |           | 1.2         | V          | 5      |

| Characteristics       |                                              | $VP = 5V, I_O = 0.4 \text{ mA}$     | 0          |           | 0.5         | V          | 5      |

|                       | Logic I Voltage                              | $VP = 12V, I_O = -0.5 \text{ mA}$   | 10.8       | _         | 12.0        | v          | 5      |

|                       |                                              | $VP = 5V, I_O = -0.2 \text{ mA}$    | 4.5        |           | 5.0         | v          | 5      |

|                       | Tri-State Leakage                            | _                                   |            | _         | 10.0        | uA         |        |

| Aiscellaneous         | CMOS Latch-up Voltage                        | _                                   | 20         | _         | _           | ν          | 6      |

| Characteristics       | SIGNAL IN Input Impedance                    | F = 1 kHz,<br>paralleled with 15 pF | 100k       | _         | _           | ohms       |        |

| Power<br>Requirements | Supply Current                               | VP = 12V<br>VP = 5V                 | _          | 17<br>6   | 40<br>18    | mA<br>mA   |        |

|                       | Power Dissipation (Outputs Open)             | VP = 12V<br>VP = 5V                 | _          | 204<br>30 | 480<br>90   | mW<br>mW   | 7      |

|                       | Power Supply Wide Band Noise                 |                                     |            |           | . •         |            |        |

|                       | (A=0, B=0)                                   | _                                   | _          | _         | 10          | mVpp       |        |

#### Notes:

- 1. With an ambient temperature of 25 °C, the signal duration and signal interval at minimum, and the signal frequency deviation and twist at maximum. The unit "dBm" refers to decibels above or below a reference power of one milliwatt into a 600-ohm load. (For example, -24 dBm equals 49 mVrms.)

- 2. Twist is defined as the ratio of the level of the high-frequency DTMF component to the level of the low-frequency DTMF component.

- 3. With an ambient temperature of 25 °C, the signal level at A + 5, the signal frequency deviation and twist at 0, and the signal applied 50 ms off and 50 ms on. The A level is the minimum detect level selected.

- 4. With the signal duration and signal interval at minimum, and the signal frequency deviation and twist at maximum. The A level is the minimum detect level selected.

- 5. Logic levels shown are referenced to VND.

- 6. Power supply excursions above this value can cause device damage.

- 7. For an ambient temperature of 25 ° C.

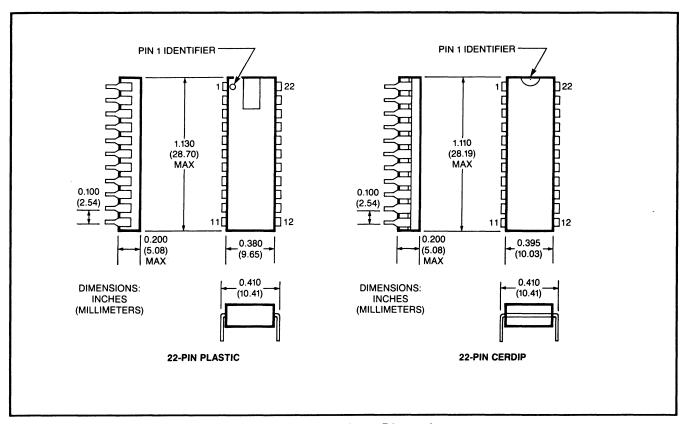

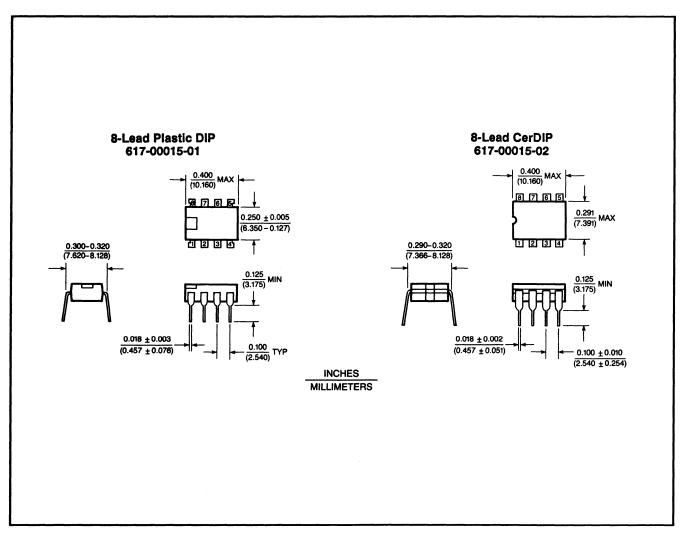

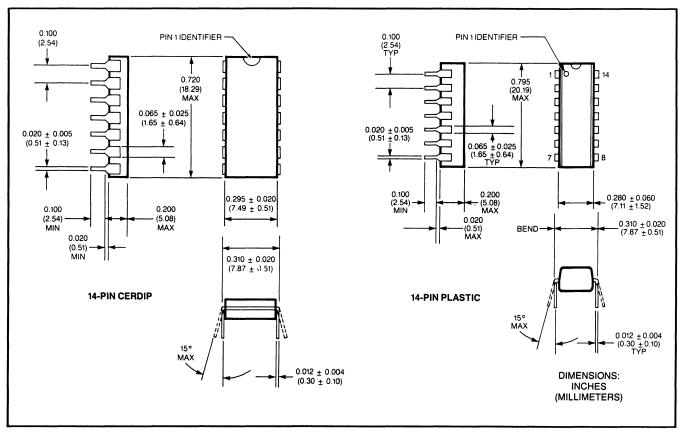

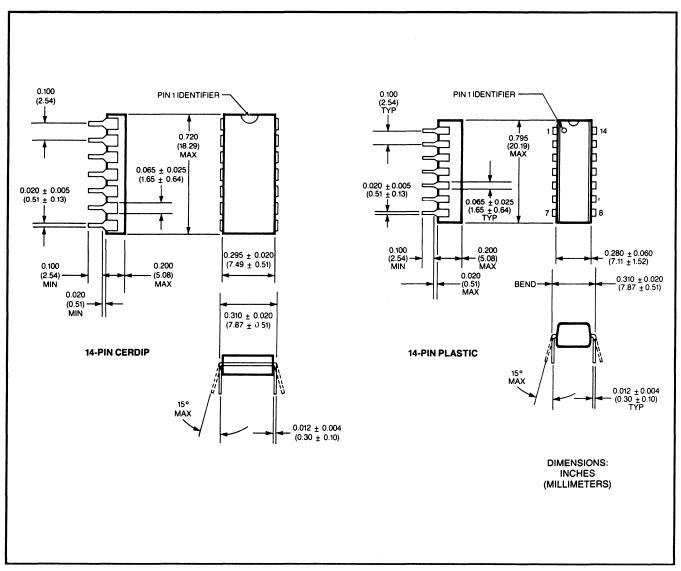

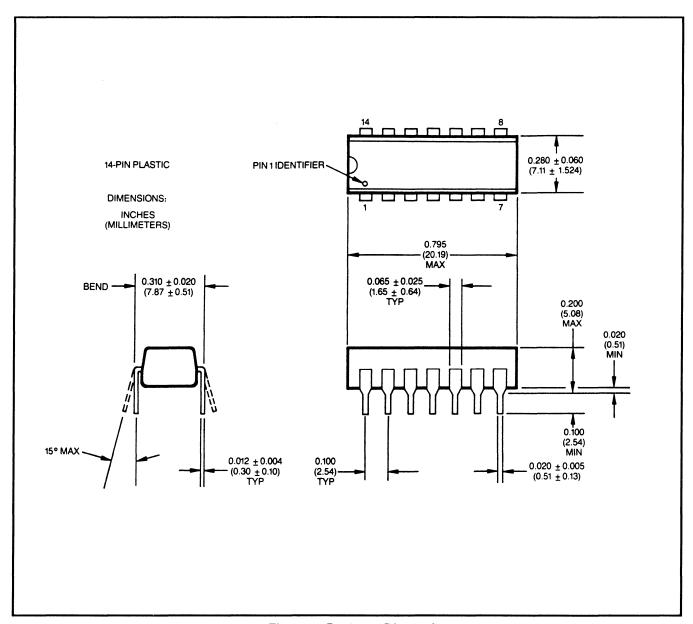

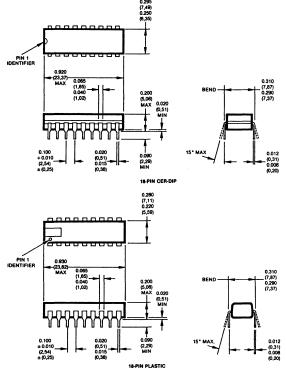

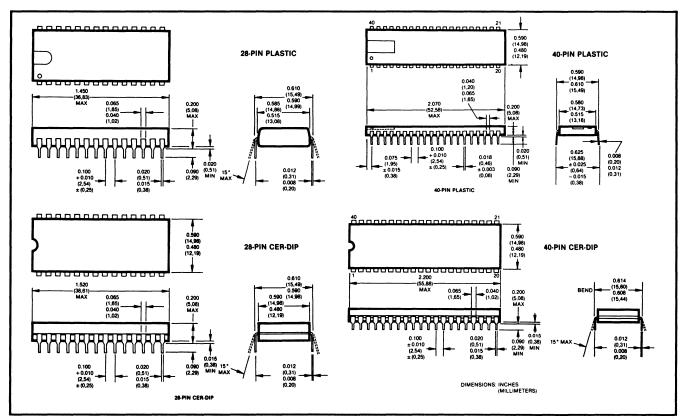

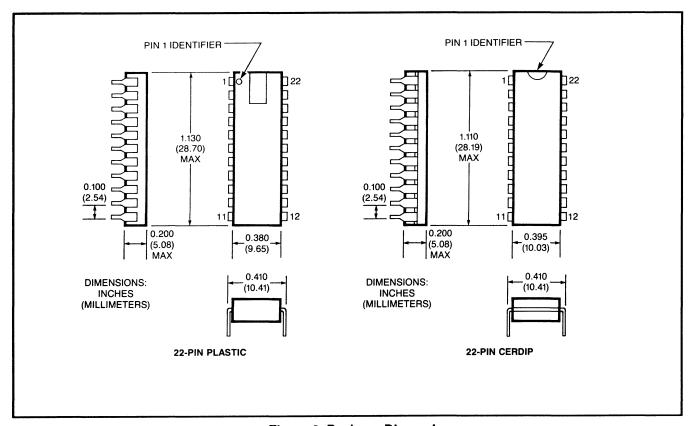

Figure 8 Package Dimensions

### M-957-02 DTMF RECEIVER

The Teltone M-957-02 (see Figure 1) combines switched-capacitor and digital frequency measuring techniques to decode Dual-Tone Multifrequency (DTMF) signals to four-bit binary data. Dial tone rejection and 60-Hz noise rejection filters are built in. Fabricated as a monolithic integrated circuit using low-power CMOS processing, the M-957-02 is packaged in a 22-pin DIP and operates from a single 5-volt DC supply, as distinguished from the M-957-01 which operates from a wide 5- through 12-volt supply. An inexpensive 3.58-MHz television crystal and resistor are the only external components required. High system density may be achieved by using the clock output of one crystal-connected receiver to drive the time bases of additional receivers.

The SIGNAL IN input to the M-957 (see Figure 2) interfaces readily to telephone lines, radio receivers, tape players, and other DTMF signal sources. Inpus A and B control sensitivity to a maximum of -38 dBm at 5 V, while the 12/16 input determines the signals to be detected. The input stages of the M-957 filter out dial tone and noise, split the signal into its high- and low-frequency components, and hard-limit each component to provide automatic gain control. Four discriminators in each group then detect the individual tones. Postprocessing stages of the M-957 time the tone durations and store binary data for outputting as determined by the HEX

input. The STROBE output is activated by the presence of valid data in the output register and cleared by the detection of a valid end-of-signal pause or by the CLEAR input. An early signal presence indicator, BD, facilitates applications requiring tone blocking. The data outputs operate with simple logic circuits or microprocessors, and are three-state enabled to facilitate bus-oriented architectures.

#### **Features**

- Complete DTMF receiver in 22-pin DIP (plastic or CerDIP)

- Decodes all 16 DTMF digits

Figure 1 Pin Diagram

Figure 2 Block Diagram

- Excellent dial tone and speech immunity

- Meets telephone impulse noise immunity standards

- Digitally selectable sensitivity to -38 dBm

- Selectable 4-bit hexadecimal or binary coded 2 of 8 output

- Fabricated using low-power CMOS technology

- Operates on single DC supply

- Uses inexpensive 3.58-MHz crystal

- Three-state outputs

#### **Applications**

- Central office products

- PBX and key systems

- Radio telephones

- Remote control and monitoring devices

- Computer data entry systems

#### **Table 1 Pin Functions**

| Pin                 | Function                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| SIGNAL IN           | DTMF input. Timings are shown in Figure 3. Internally biased so that the input signal may be AC coupled, SIGNAL IN also permits DC coupling as long as the input voltage does not exceed the positive supply. Proper coupling is shown in Figure 5. See Table 2 for the frequency pairs associated with each DTMF signal. |  |  |  |  |  |

| 12/16               | DTMF signal detection control. When 12/16 is at logic "1", the M-957 detects the 12 most commonly used DTMF signals (1 through #). When 12/16 is at logic "0", the M-957 detects all 16 DTMF signals (1 through D).                                                                                                       |  |  |  |  |  |

| A, B                | Binary DTMF signal sensitivity control inputs. A and B select the sensitivity of the SIGNAL IN input to a maximum of $-31$ dBm.                                                                                                                                                                                           |  |  |  |  |  |

| D3, D2, D1. D0      | Data outputs. When enabled by the OE input, the data outputs provide the code corresponding to the detected digit in the format programmed by the HEX pin. See Table 2. The data outputs become valid after a tone pair has been detected and are cleared when a valid pause is timed. Timings are shown in Figure 3.     |  |  |  |  |  |

| OE                  | Output enable. When OE is at logic "1", the data outputs are in the CMOS push/pull state and represent the contents of the output register (see Figure 2). When OE is driven to logic "0", the data outputs are forced to the high-impedance or "third" state. Timings are shown in Figure 3.                             |  |  |  |  |  |

| нех                 | Binary output format control. When HEX is at logic "1", the output of the M-957 is full, 4-bit binary. When HEX is at logic "0", the output is binary coded 2-of-8. Table 2 shows the output codes.                                                                                                                       |  |  |  |  |  |

| STROBE              | Valid data indication. STROBE goes to logic "1" after a valid tone pair is sensed and decoded at the data outputs. STROBE remains at logic "1" until a valid pause occurs or the CLEAR input is driven to logic "1", whichever is earlier. Timings are shown in Figure 3.                                                 |  |  |  |  |  |

| CLEAR               | STROBE control. Driving CLEAR to logic "1" forces the STROBE output to logic "0". When CLEAR is at logic "0", STROBE is forced to logic "0" only when a valid pause is detected. Tie to VNA or VND when not used.                                                                                                         |  |  |  |  |  |

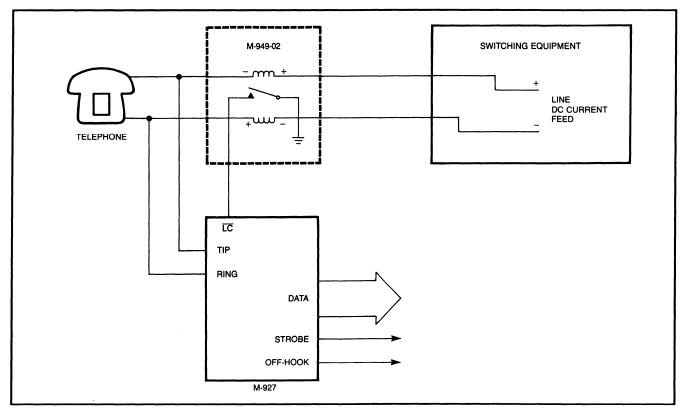

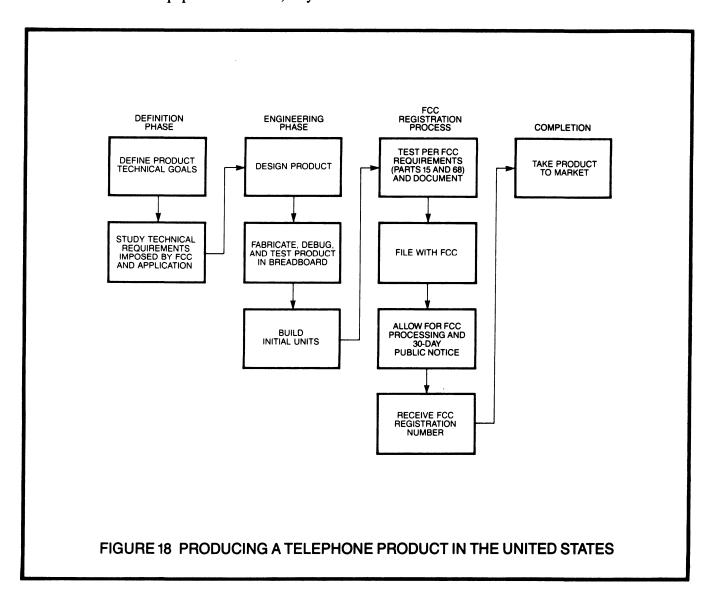

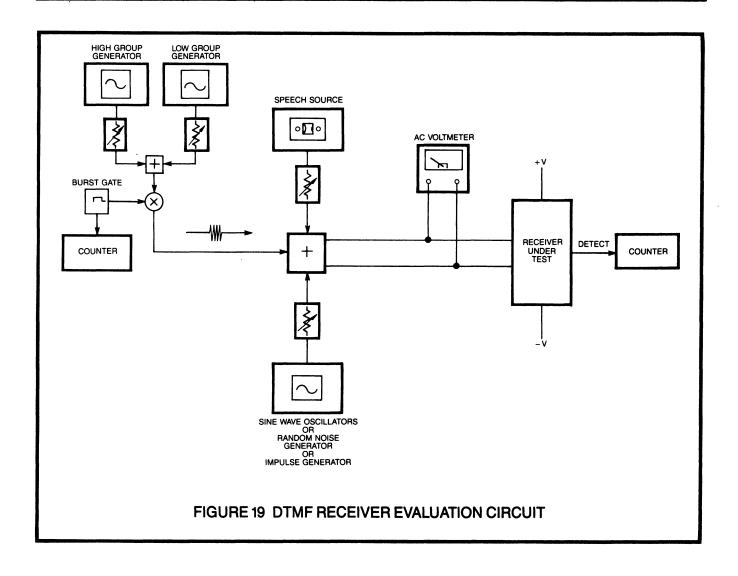

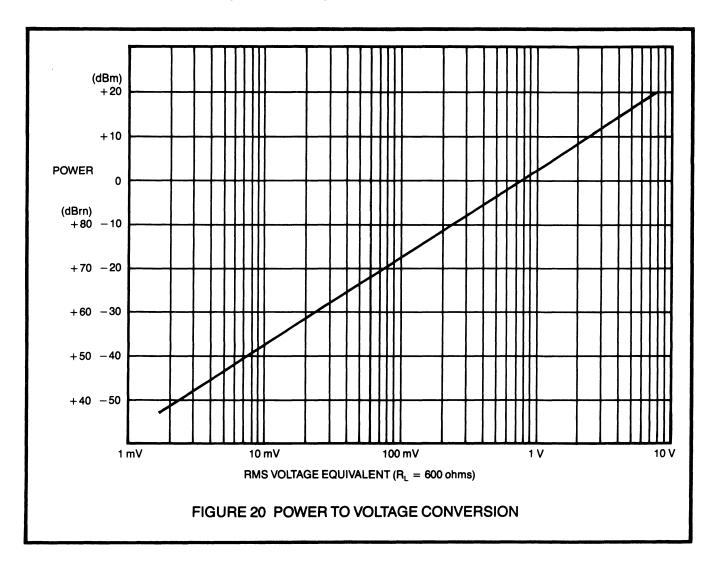

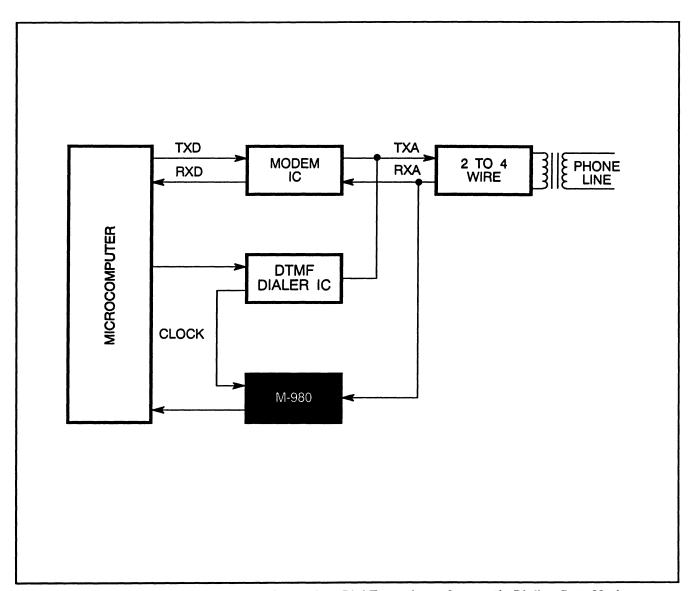

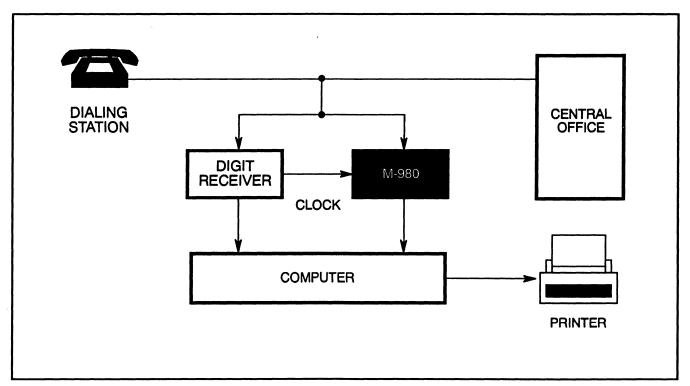

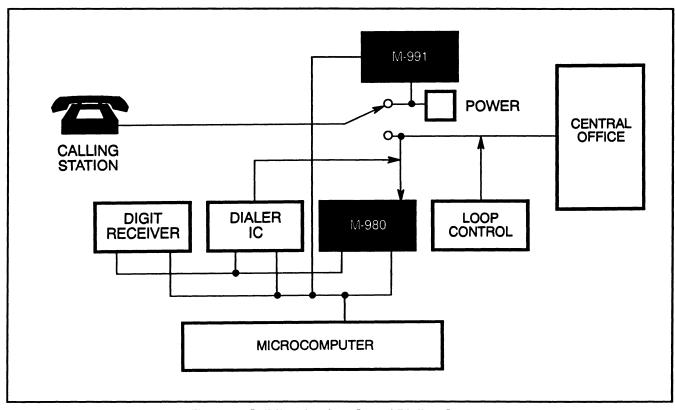

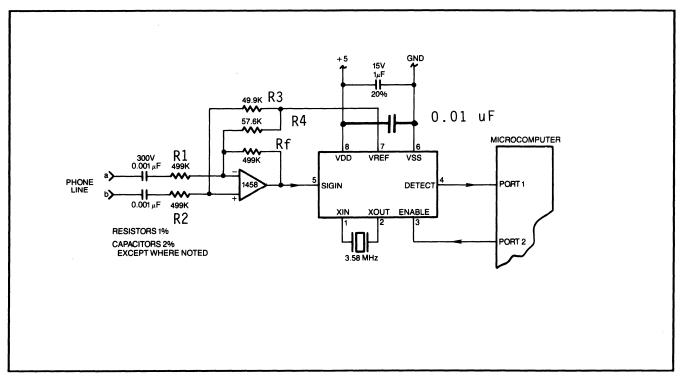

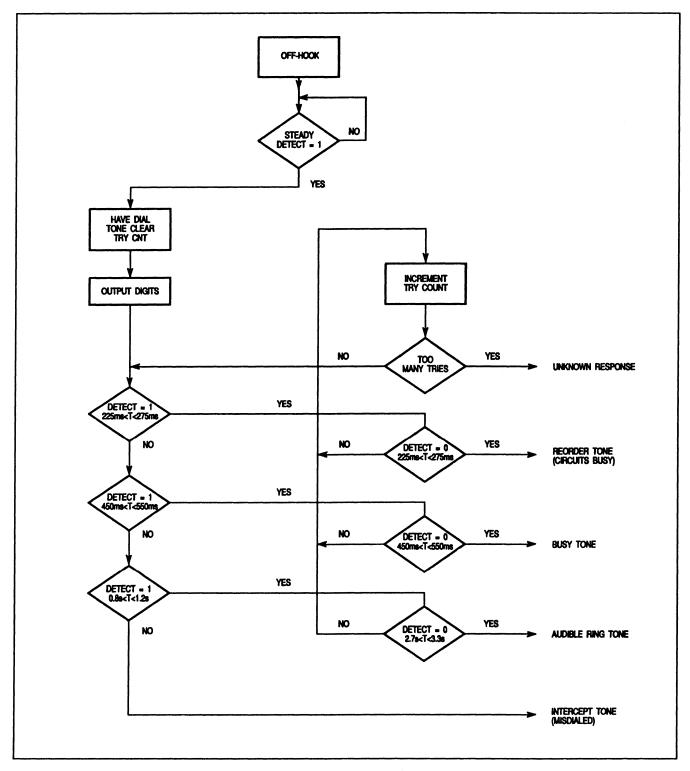

| BD                  | Early signal presence output. BD indicates that a possible signal has been detected and is being validated. As shown in Figure 3, BD precedes STROBE and the data outputs.                                                                                                                                                |  |  |  |  |  |